「業界最高」のメモリ密度 ルネサスの車載SoC向け3nm TCAM技術:ISSCC 2026で発表(1/2 ページ)

ルネサス エレクトロニクス、3nm FinFETプロセスを用いたコンフィギュラブルなTCAM(Ternary Content Addressable Memory)技術を発表した。TCAMの高密度化と低消費電力化、機能安全の強化に貢献し、車載SoC(System on Chip)にも適用できる。ルネサスはこの成果を「International Solid-State Circuits Conference(ISSCC) 2026」で発表した。

ルネサス エレクトロニクス(以下、ルネサス)は2026年2月18日、3nm FinFETプロセスを用いたコンフィギュラブルなTCAM(Ternary Content Addressable Memory)技術を発表した。同技術はTCAMの高密度化と低消費電力化、機能安全の強化に貢献し、車載SoC(System on Chip)にも適用できる。

ルネサスはこの成果を「International Solid-State Circuits Conference(ISSCC) 2026」(2026年2月15〜19日、米国カリフォルニア州サンフランシスコ)で発表した。

大容量化で周辺回路増大や消費電力が課題に

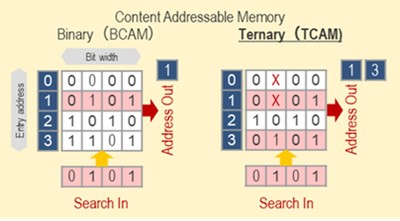

TCAMは、メモリ内部に蓄えた全情報から入力値に合致するデータを1サイクルで探し出すなど、検索に特化したメモリだ。RAMではアドレスを指定してデータを出力するのに対し、CAMではデータを入力してアドレスを出力する。

車載用途では、センサーから得た情報をどのプロセッサに届けるかなどを判断する通信制御で用いられる。ルネサスでは現在、7nmプロセスまでのIP(Intellectual Property)としてTCAMを提供している。

5Gの普及やクラウド/エッジコンピューティングの拡大に伴ってトラフィックが急増する中、TCAMには246ビット×4096エントリー級の大規模かつ多様な構成が求められるようになった。しかし、ハードマクロに依存した従来の大容量化では、バンクやリピーターの増加によって周辺回路面積が大きくなり、タイミング収束も難しくなるという課題があった。また、検索時の消費電力も増加する。さらに、これを車載用途で利用するには、機能安全をより強化することも求められる。

柔軟な構成変更で「業界最高」の高密度化

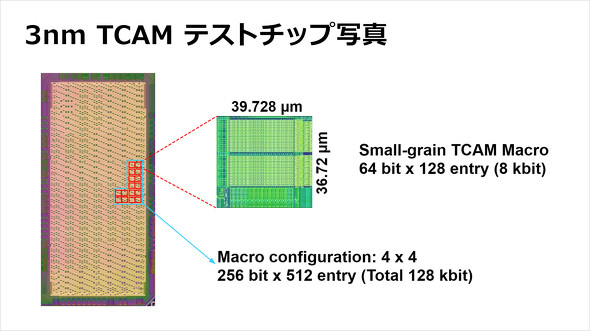

ルネサスが新しく開発したTCAMハードマクロは、検索キー幅8〜64ビット、エントリー深さ32〜128という小粒度のメモリコンパイラとしてサポートする。このハードマクロと、ツールによるソフトマクロ自動生成技術を組み合わせることで、単一マクロとして広範囲をカバーするコンフィギュラブルな構成が可能で、246ビット×4096エントリーのような大きな構成にも対応できる。これによって、1チップ内で多様なTCAM構成を柔軟かつ高密度に実現できる。ルネサスによると、メモリ密度は5.27Mビット/mm2で「業界最高レベル」だという。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- キオクシア25年度 驚異の決算 Q4純利益は前年比30倍

- iPhone好調で過去最高も、「世界一」維持へ動くソニー半導体

- 加賀電子が新光商事にTOB、完全子会社化へ

- JDI、25年度Q4は4年ぶり黒字 上場廃止は「必ず阻止」

- SiC LSIの事業化に挑む 28年以降ADCのサンプル出荷へ

- AIの「トンデモ判断」で本番DBが全飛び! 他山の石にしたいAIコーディングの落とし穴

- サンケン電気26年3月期は赤字転落 中国の「自前主義」響く

- Cerebrasが上場 NVIDIA対抗馬の「試金石」となるか

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk