インターポーザに複数のシリコンダイを近接して並べる2.5次元集積化:福田昭のデバイス通信(507) TSMCが解説する最新のパッケージング技術(4)

前回に続き、「IEDM 2025」におけるTSMCの講演内容を紹介する。TSMCの2.5次元パッケージング技術「CoWoS(Chip on Wafer on Substrate)」において、インターポーザを低コスト化する技術を解説する。

高性能ロジックのチップレットは近接配置が必須

2025年12月に開催された国際学会IEDMのショートコース(技術解説)で、シリコンファウンドリー最大手のTSMCが最新のパッケージング技術を説明した。講演のタイトルは「Advanced Packaging and Chiplet Technologies for AI and HPC Applications(AIおよびHPCに向けた先端パッケージング技術と先端チップレット技術)」、講演者はAdvanced Package Integration Division R&DのディレクターをつとめるJames Chen氏である。大変に参考となる内容だったので、その一部をシリーズでご紹介している。ただし講演内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演内容を筆者が適宜、補足してある。あらかじめご了承されたい。

講演「Advanced Packaging and Chiplet Technologies for AI and HPC Applications(AIおよびHPCに向けた先端パッケージング技術と先端チップレット技術)」のアウトライン[クリックで拡大] 出所:TSMC(IEDM 2025のショートコース(番号SC1-5)で公表された講演スライドから)

講演「Advanced Packaging and Chiplet Technologies for AI and HPC Applications(AIおよびHPCに向けた先端パッケージング技術と先端チップレット技術)」のアウトライン[クリックで拡大] 出所:TSMC(IEDM 2025のショートコース(番号SC1-5)で公表された講演スライドから)タイトルスライドの次に示されたアウトラインは、「AI and HPC Market Outlook(AIとHPCの市場を展望)」「Advanced Package Technology Evolutions(先進パッケージ技術の進化)」「System-Technology Co-Optimization (STCO)(システムと製造の協調最適化)」「Emerging Advanced package technology(次世代の先進パッケージ技術)」「Summary(まとめ)」となっていた。

本シリーズの前々回と前回は、アウトラインの第2項「Advanced Package Technology Evolutions(先進パッケージ技術の進化)」に相当する部分を述べた。今回はその続きとなる。

前回でも述べたように、複数のミニダイ(チップレット)を集積化する技術としては中間基板(インターポーザ)を利用する手法(2.5Dパッケージング)が高性能サブシステムに適している。高性能コンピューティング(HPC)や人工知能(AI)などのハイエンドサーバでは、プロセッサモジュールに2.5Dパッケージングが標準的に使われる。その代表が、TSMCが開発した「CoWoS(Chip on Wafer on Substrate)」(筆者注:「コワース」と呼ばれることが多い)だ(参考記事:「10年で5世代の進化を遂げた高性能パッケージング技術「CoWoS」(前編)」)。

CoWoSでは、中間基板(インターポーザ)と微細な配線(「再配線層(RDL)」と呼ばれる)によって複数のミニダイ同士をぎりぎりまで近づけて配置できるようにした。ミニダイ間を接続する配線の距離が極めて短くなるとともに、寸法当たりの接続数が大幅に増加する。短い配線は高速伝送に適しており、接続数の増加はデータ転送速度(帯域幅)を大きく高める。

Siインターポーザの急拡大とコスト上昇が代替技術の採用を促す

CoWoSのインターポーザには当初、シリコン基板(Siインターポーザ)が使われた。シリコン基板は熱膨張係数がミニダイ(チップレット)と同じで、温度変化による歪みが生じない。パッケージ基板(樹脂基板)とシリコン基板の間で生じる熱歪みは、接続電極であるマイクロバンプが緩和する。

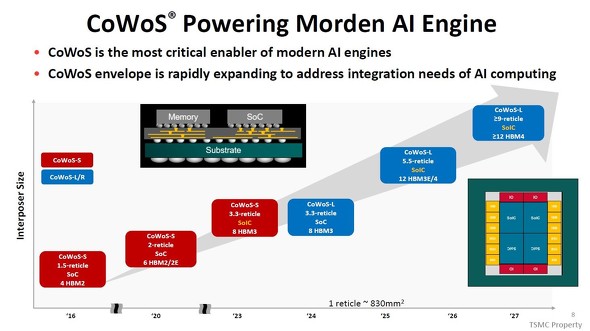

Siインターポーザは優れた特性を有しているものの、実装基板としては面積当たりのコストが高いという弱点を抱えていた。Siインターポーザの面積は2016年にレチクル(約830mm2)の1.5倍だったのが、2023年にはレチクルの3.3倍と7年で2倍強に拡大した。

そこでTSMCはCoWoSのインターポーザにおけるコスト上昇を緩和するため、2種類のインターポーザ技術を追加した(参考記事:「Siインターポーザを樹脂基板に変更した低コスト版の「CoWoS」」)。1つはRDLをインターポーザとする「CoWoS-R(RDL interposer)」、もう1つはシリコンブリッジ(「LSI(Local Silicon Interconnect)」とTSMCは呼称)とRDLインターポーザを組み合わせた「CoWoS-L(LSI+RDL interposer)」である。シリコンブリッジは特に、接続数の多いミニダイを近接して置くために利用される。

HPC/AI向けハイエンドプロセッサモジュールでSiインターポーザを置き換えたのは、「CoWoS-L」技術だ。レチクルの3.3倍となるインターポーザから採用が始まった。レチクルの5.5倍とさらに大きなインターポーザにも「CoWoS-L」が使われた。将来は、レチクルの9倍以上の面積となるインターポーザにも、「CoWoS-L」を採用する計画である。なお従来のSiインターポーザによるCoWoSは、「CoWoS-S(Si interposer)」と表記を改めて区別した。

2.5Dパッケージング技術「CoWoS(Chip on Wafer on Substrate)」の進化。横軸は年(西暦)、縦軸はインターポーザ(中間基板)の大きさ[クリックで拡大] 出所:TSMC(IEDM 2025のショートコース(番号SC1-5)で公表された講演スライドから)

2.5Dパッケージング技術「CoWoS(Chip on Wafer on Substrate)」の進化。横軸は年(西暦)、縦軸はインターポーザ(中間基板)の大きさ[クリックで拡大] 出所:TSMC(IEDM 2025のショートコース(番号SC1-5)で公表された講演スライドから)⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

複数のミニダイ(チップレット)を1つのパッケージに収容する

複数のミニダイ(チップレット)を1つのパッケージに収容する

2025年12月に開催された国際学会IEDMにおける、TSMCの講演を解説するシリーズ。今回は、前回に続き、「先進パッケージ技術の進化」を取り上げる。分割した複数のミニダイを同一パッケージに収容する際の、3つの接続手法を解説する。 AIサーバの高性能化に不可欠となった先進パッケージング技術

AIサーバの高性能化に不可欠となった先進パッケージング技術

2025年12月の国際学会IEDMで、TSMCが最新のパッケージング技術について講演した。本シリーズは、その内容の一部を紹介する。 メモリとストレージの動向を示す11個のキーワード(前編)

メモリとストレージの動向を示す11個のキーワード(前編)

2025年8月に開催された「FMS」の講演を紹介するシリーズ。今回はメモリとストレージの市場アナリストとして知られるJim Handy氏の講演を前後編でご紹介する。 2026年のHBM市況、カギを握るのは最新世代「HBM4」

2026年のHBM市況、カギを握るのは最新世代「HBM4」

2025年8月に開催された「FMS(the Future of Memory and Storage)」の一般講演を紹介するシリーズ。今回はTrendForceのアナリストであるEllie Wang氏の講演を取り上げる。広帯域メモリ(HBM)の生産能力や容量、価格を予測する。 創刊前の20年間(1985年〜2005年)で最も驚いたこと:1985年の「不可能」二題

創刊前の20年間(1985年〜2005年)で最も驚いたこと:1985年の「不可能」二題

EE Times Japan 創刊20周年に合わせて、半導体業界を長年見てきたジャーナリストの皆さまや、EE Times Japanで記事を執筆していただいている方からの特別寄稿を掲載しています。今回は、40年以上にわたり半導体技術/電子技術を見守り、フリーの技術ジャーナリストとして活躍されている福田昭氏にご寄稿いただきます。EE Times Japan創刊からさらに20年さかのぼり、1985年の話からスタートします。 キオクシアの年度業績、3年ぶりの黒字転換で過去2番目の営業利益を計上

キオクシアの年度業績、3年ぶりの黒字転換で過去2番目の営業利益を計上

キオクシアホールディングスの2024会計年度通期(2024年4月〜2025年3月)の決算概要を説明する。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- キオクシア25年度 驚異の決算 Q4純利益は前年比30倍

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- JDI、25年度Q4は4年ぶり黒字 上場廃止は「必ず阻止」

- iPhone好調で過去最高も、「世界一」維持へ動くソニー半導体

- 加賀電子が新光商事にTOB、完全子会社化へ

- 「技術ナンバーワンであり続ける」 ソニーセミコンCTOが語る技術戦略

- SiC LSIの事業化に挑む 28年以降ADCのサンプル出荷へ

- AIの「トンデモ判断」で本番DBが全飛び! 他山の石にしたいAIコーディングの落とし穴

- サンケン電気26年3月期は赤字転落 中国の「自前主義」響く

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk