第29回 MOSFETを使ってオペアンプを設計:Analog ABC(アナログ技術基礎講座)(1/3 ページ)

今回は、これまでに紹介してきた幾つかの基本回路と差動対を組み合わせて、MOSFETを使ったオペアンプを設計しましょう。本連載の第16〜第20回の「差動対がオペアンプに変身」シリーズと同様に、MOSFETでもオペアンプを構成しました。

前回(第28回)は、MOSFETのソース接地増幅回路の利得や応答速度を高める方法を紹介しました。

増幅回路の負荷抵抗に能動素子を使うことで、利得を高めることができます。ただ、能動素子を使うだけだと、2つのMOSFETのしきい値(Vth)のわずかなずれが、利得や動作点に大きな影響を与えたり、応答速度が遅くなるといった欠点が生まれます。そこで前回は、しきい値が変わってもMOSFETを流れる電流値が同じになるように、カレントミラーを組み合わせました。

これまでに学んだ複数の回路を活用

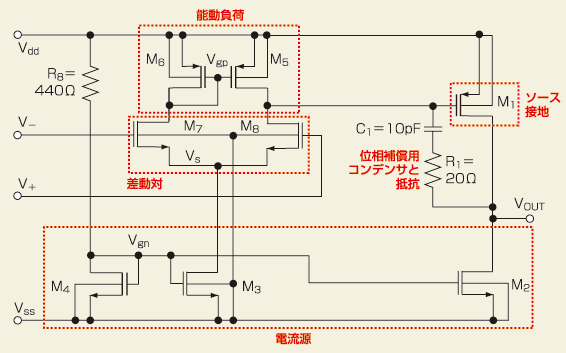

今回は、これまでに紹介してきた幾つかの基本回路と差動対を組み合わせて、MOSFETを使ったオペアンプを設計しましょう。本連載の第16〜第20回の「差動対がオペアンプに変身」シリーズと同様に、MOSFETでもオペアンプを構成しました(図1)。

図1をじっくりと見てください。M2とM3、M4が電流源で、M7とM8が差動対、M5とM6が能動負荷、M1がソース接地アンプ、C1が位相補償用コンデンサです。本連載第20回の「差動対がオペアンプに変身(5)〜コンデンサを追加して位相補償〜」に記載した図1と同じ回路を、MOSFETで構成した格好です*1)。

本連載でこれまで解説してきたことの重複になりますが、図1の各回路ブロックの役割を簡単に紹介しましょう。まず、差動対のM7とM8は、入力電圧の差分のみを増幅し、同相成分を除去する働きをします(これを「同相除去」と言います)。入力した信号の中から同相の信号を取り除き、後段に雑音として伝わるのを防止しています。

電流源のM2とM3、M4は、上に説明した差動対の動作の元ともいえる回路で、差動対のソースの電圧Vsが変化したときにも、流れる電流が変化しないので、同相信号を後段の回路に伝えることなく、差動信号のみを増幅できるのです。オペアンプICのデータシートには、同相除去比(CMRR:Common Mode Rejection Ratio)という指標が記載されているので確認してみてください。

能動負荷のM5とM6は、増幅器の利得を高めるためのものです。M5とM6はカレントミラーなので、M6に流れる電流値がそのままM5にも流れます。電流源の出力インピーダンスは非常に高いので、差動対M8に非常に高い負荷抵抗が接続されたのと同じ状況になります。結果、能動負荷を使うことで、高い利得を得ることができるのです。

ソース接地のM1は、出力VOUTの動作範囲を広めるとともに、電流源M2を負荷として接続することでさらに利得を高める効果を生み出しています。

最後に、位相補償用コンデンサC1はオペアンプを安定して動作させるために、オープンループ(Open Loop)時の位相余裕を確保する目的で入れてあります。コンデンサC1と直列の抵抗R1によって、位相戻し回路を構成し、過剰な位相遅れを補正しています。

いずれも、本連載でこれまで解説してきた基本回路です。オペアンプは、差動対と基本回路をうまく組み合わせることで構成できるのです。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

図1 MOSFETを使ったオペアンプ これまでの連載で紹介してきた、差動対や電流源、能動負荷、ソース接地といったさまざまな要素回路を組み合わせて、オペアンプを構成しました。

図1 MOSFETを使ったオペアンプ これまでの連載で紹介してきた、差動対や電流源、能動負荷、ソース接地といったさまざまな要素回路を組み合わせて、オペアンプを構成しました。