第31回 MOSFETのオペアンプを改善〜FETを変えず回路の工夫で特性向上〜:Analog ABC(アナログ技術基礎講座)(1/2 ページ)

今回は、前回に続いて、MOSFETを使ったオペアンプの特性の改善を進めます。前回は、オペアンプをボルテージフォロアとして使うと、出力電圧が電源電圧まで達しない原因を説明し、その対策として出力段のトランジスタの寸法を変えるという方法を紹介しました。今回は、トランジスタの寸法を変更しない改善方法を解説します。

今回は、前回(第30回)に続いて、MOSFETを使ったオペアンプの特性の改善を進めます。前回は、オペアンプをボルテージフォロアとして使うと、出力電圧が電源電圧まで達しない原因を説明し、その対策として出力段のトランジスタの寸法を変えるという方法を紹介しました。しかし、トランジスタの寸法の変更は、チップの寸法を増やしてしまったり、寄生容量が増加してオペアンプの特性を劣化させてしまうという側面もあります。

今回は、出力電圧が電源電圧まで達しないという現象の改善に続いて、出力電圧がグラウンド電圧に達しないという現象の改善に取り掛かろうと考えていましたが、予定を変更します。電源側の対策として、トランジスタの寸法を変更しない方法を解説します。

差動対の負荷を変更

これまで設計を続けてきた回路(第30回の図3)では、差動対の2つのトランジスタX7とX8の接点部分の電圧Vsと、トランジスタX8のドレイン電圧Voがぶつかることが、電源側の動作を制限していました。

つまり、出力段のゲート電圧はもっと下がれる状態なのに、入力トランジスタのゲート電圧やソース電圧が上に上がってきてしまい、両者がぶつかって出力電圧が電源電圧まで達せずにいました。詳しくは、本連載の第30回を参考にしてください。このような状態を改善するには、出力段のゲート電圧を可能な限りグラウンド電圧にまで下げられる回路を設計することが効果的です。

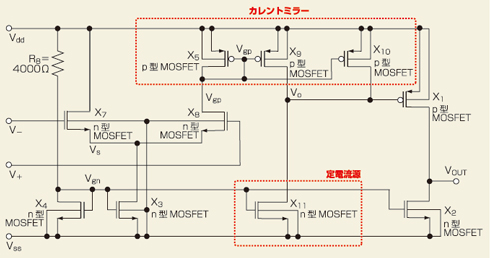

それでは、詳しく説明しましょう。図1に今回改善を進めたオペアンプを示しました。前回の回路からの変更点は、差動対の負荷の作り方です。前回は、カレントミラーのX5とX6が能動負荷として差動対に接続されていましたが、これを図1のように変更します。赤い枠で囲んだ「カレントミラー」と記載した部分に注目してください。

図1 さらに特性改善を進めたオペアンプ 前回はMOSFETの寸法を調整することで、出力電圧が電源電圧に達しないという課題を改善しました。今回は、回路の工夫で改善を試みます。具体的には図中の赤い枠で、「カレントミラー」と「定電流源」と記載した部分が前回の回路と異なります。

図1 さらに特性改善を進めたオペアンプ 前回はMOSFETの寸法を調整することで、出力電圧が電源電圧に達しないという課題を改善しました。今回は、回路の工夫で改善を試みます。具体的には図中の赤い枠で、「カレントミラー」と「定電流源」と記載した部分が前回の回路と異なります。p型カレントミラーのX5とX9、X10を差動対の片方のMOSFET(X8)のみに接続し、能動負荷にはn型の電流源として動作するX11を接続します。このようにしておけば、出力段のゲート電圧Voは、入力段の差動対X7とX8のソース電圧Vsが高くなったとしても、ぶつかることはありません。なお、p型カレントミラーのX10は、カレントミラー部の吐き出し電流量を、能動負荷の吸い込み電流量(X11の電流)よりも大きくして、出力段のゲート電圧Voを十分に電源側に張り付かせるために挿入しています。

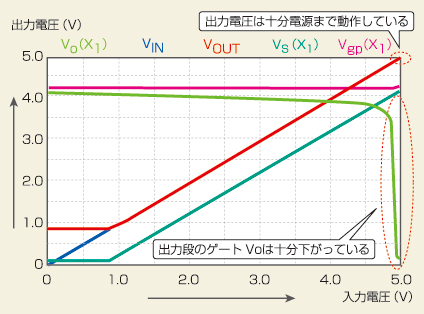

図2 今回設計したオペアンプの直流(DC)特性 オペアンプをボルテージフォロア接続し、直流特性をシミュレーションしました。もくろみ通りに、出力段のゲート電圧Voはグラウンド電圧付近まで下がっています。これに伴って、出力電圧は十分に電源電圧まで達するようになりました。

図2 今回設計したオペアンプの直流(DC)特性 オペアンプをボルテージフォロア接続し、直流特性をシミュレーションしました。もくろみ通りに、出力段のゲート電圧Voはグラウンド電圧付近まで下がっています。これに伴って、出力電圧は十分に電源電圧まで達するようになりました。実際に、改善したオペアンプをボルテージフォロア接続し、直流(DC)特性を確認してみましょう。解析結果を図2に示しました。もくろみ通りに、出力段のゲート電圧Voはグラウンド電圧付近まで下がっています。横軸の入力電圧が5Vの付近で、赤い枠で囲った部分です。前回より小さい負荷抵抗である1kΩを接続しているのにもかかわらず、出力電圧は十分に電源電圧にまで達しています。当初の目的通り、M0FETの寸法を調整せずに、入出力特性を改善できました。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- 「世界2位」は実現するか、ローム、東芝、三菱電機とデンソーの選択は

- Musk氏は「半導体製造の再定義」を目指すのか

- 世界半導体市場は26年2月に大幅成長、日本のみ9カ月連続マイナスに

- ローム、8インチSiC MOSFET開発の技術目標を2年前倒しで達成

- 米Waymoの世界展開は東京から 「開始まで何年もかからない」

- 300mmファブ装置の投資額、2年連続で2桁成長へ

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- Intelがアイルランド工場を完全子会社化、Apolloから49%買い戻し

- シャープ新社長は海外事業出身 鴻海と連携で「新たな成長ステージへ」