第31回 MOSFETのオペアンプを改善〜FETを変えず回路の工夫で特性向上〜:Analog ABC(アナログ技術基礎講座)(2/2 ページ)

n型とp型のしきい値の差を考慮

これで問題はすべて解決と思いたいのですが、実際の回路ではさらなる改善が必要です。それは、p型MOSFETのしきい値電圧が、n型MOSFETのしきい値電圧よりも高いことが一般的だからです。今までの計算は、n型とp型のしきい値電圧を0.7Vといずれも同じ値に設定していました。

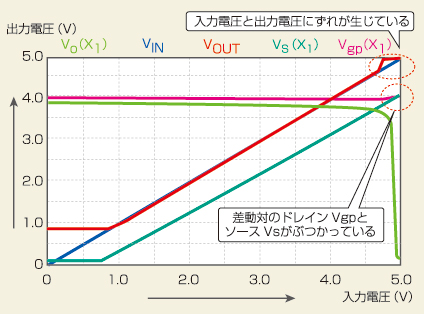

p型MOSFETのしきい値電圧を現実に則した0.9Vに設定してシミュレーションした結果を、図3に示しました。差動対X8のドレイン電圧Vgp(ピンクのライン)と、ソース電圧Vs(灰色のライン)がぶつかってしまい、入力電圧VIN(青い色のライン)と出力電圧VOUT(赤い色のライン)にずれが生じています。これは、ボルテージフォロアとしての動作がうまくできなくなったことを意味しています。

このような現象を改善するには、どのような対策を採ればよいでしょうか。差動対のドレイン電圧Vgpをできるだけ電源に近づける必要があります。ただ、差動対のドレインには、p型MOSFETが接続されています。従って、p型MOSFETのドレイン電圧Vgsの分の電圧降下は避けられないと考えてしまいがちですが……。実はこれを回避するお勧めの回路があります。

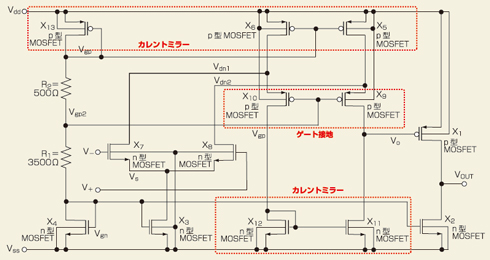

図4に、その回路を示しました。図1のオペアンプに比べると少し複雑になっています。変更点は、図1のオペアンプにp型とn型の電流源とゲート接地回路(X9とX10)を追加したことです。

図4 n型とp型MOSFETのしきい値電圧の差を考慮したオペアンプ 図1に紹介したオペアンプに比べて、複雑になっています。変更点は、図1のオペアンプにp型とn型の電流源とゲート接地回路(X9とX10)を追加したことです。図中の赤い枠で示した部分に注目してください。

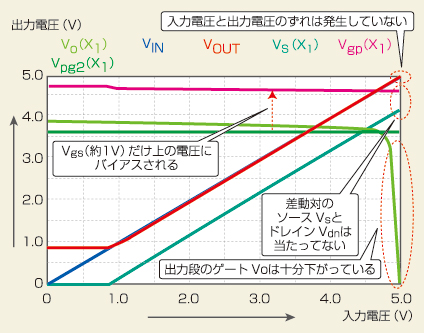

図4 n型とp型MOSFETのしきい値電圧の差を考慮したオペアンプ 図1に紹介したオペアンプに比べて、複雑になっています。変更点は、図1のオペアンプにp型とn型の電流源とゲート接地回路(X9とX10)を追加したことです。図中の赤い枠で示した部分に注目してください。ポイントとなるのは、ゲート接地回路を追加して、このソースに差動対(X7とX8)のドレインを接続したことです。図4の回路の場合、差動対のドレイン電圧であるVdn1とVdn2は、ゲート接地回路(X9とX10)のゲート電圧Vgp2より、Vgsだけ高い電圧にバイアスされます。つまり、電源電圧Vddからの電圧降下で決まっていた差動対のドレイン電圧Vgpを任意に設定できることになります。図5に、n型MOSFETとp型MOSFETのしきい値電圧の差を考慮したオペアンプの直流解析の結果を示しました。

先に説明した通り、差動対のドレイン電圧Vdn1とVdn2は、ゲート接地のゲート電圧Vgp2よりも、Vgs(約1V)だけ上にバイアスされています。従って、差動対のゲートが電源Vddに達しても、差動対のドレイン電圧(Vdn1およびVdn2)と、ソース電圧Vsの間には、まだすき間が残っています。これで、差動対は利得を失うことなく動作し、ボルテージフォロアとして電源Vddまできちんと動作できるようになりました。

次回はGND側の改善へ

今回紹介した回路では、前回のようにトランジスタの寸法を増やすことなく、入力電圧が電源電圧に達するまできちんと増幅動作をさせることができました。しかも、n型MOSFETとp型MOSFETのしきい値電圧の差も考慮してあります。実際のオペアンプではさらにさまざまな工夫を盛り込んでいます工夫を盛り込んでいます。例えば、バイアス電圧であるVgnやVgp、Vgp2の生成方法を工夫して、さまざまな要因で発生する変動やばらつきに対して安定した特性を得ています。

次回はいよいよ、グラウンド電圧側の改善に取り掛かります。CMOSのCは、Complimentary(相補的)の意味ですので、今回紹介した回路を反対にした回路を作成して合成させることで、グラウンド側も改善できるはずです。

Profile

美齊津摂夫(みさいず せつお)

1986年に大手の通信系ハードウエア開発会社に入社し、光通信向けモジュールの開発に携わる。2004年に、ディー・クルー・テクノロジーズに入社。現在は、同社の常務取締役CTO(最高技術責任者)兼プラットフォーム開発統括部長を務めている。「大学では電気工学科に所属していたのですが、学生のときにはアナログ回路の勉強を避けていました。ですから、トランジスタや電界効果トランジスタ(FET)を使ったアナログ回路の世界には、社会人になってから出会ったといっていいと思います。なぜかアナログ回路の魅力に取りつかれ、23年目になりました」。

関連記事

- Analog ABC(アナログ技術基礎講座)バックナンバー

第1回 楽しいアナログ回路設計

第1回 楽しいアナログ回路設計

「アナログ」という言葉を聞くと「古い」、「時代遅れ」、「頑固親父」なんていう印象を持つ人が多いかもしれません。アナログは「アナクロニズム(時代錯誤)」と語感が似ていることが原因かもしれませんが、アナログ回路の世界は楽しいものなのです。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- デンソー、ロームに対する株式取得提案を正式表明

- NVIDIAとメモリ3社、世界半導体売上高の42%占める

- もはや半導体メーカーの域を超えた NVIDIA最新エッジ機器を分解

- Armが半導体の自社開発に参入、AIデータセンター向けCPU発表

- キオクシアがNanyaに774億円出資、DRAM長期供給契約を締結

- 魚津はTower、砺波はNuvotonに TPSCo事業の再編を発表

- パワー半導体再編が本格化 ローム・東芝・三菱電機が協議開始へ

- 「Renesas 365」がついに始動 「不可能だった規模」の検証、数分で

- ソニー・ホンダモビリティ、EV「AFEELA」開発中止

- イラン戦争の長期化が半導体業界に及ぼす深刻な影響

図3 n型とp型MOSFETのしきい値電圧の差を考慮したシミュレーション結果 電源電圧(5V)付近では、入力電圧と出力電圧にずれが生じてしまっています。さらに改善をする必要がでてきました。

図3 n型とp型MOSFETのしきい値電圧の差を考慮したシミュレーション結果 電源電圧(5V)付近では、入力電圧と出力電圧にずれが生じてしまっています。さらに改善をする必要がでてきました。 図5 n型とp型MOSFETのしきい値電圧の差を考慮したオペアンプのシミュレーション結果 差動対のソース電圧Vsとドレイン電圧Vdnがぶつかっておらず、入力電圧と出力電圧にずれは発生していません。

図5 n型とp型MOSFETのしきい値電圧の差を考慮したオペアンプのシミュレーション結果 差動対のソース電圧Vsとドレイン電圧Vdnがぶつかっておらず、入力電圧と出力電圧にずれは発生していません。