グラフェン利用のRFてい倍器IC、IBMがCMOS互換プロセスで製造:材料技術 グラフェン

次世代の半導体材料の1つとして注目を集めるグラフェン。ICチップの量産性に課題があるものの、その克服に向けた技術の開発が少しずつ進んでいる。IBMはシリコン材料を使うCMOSプロセスに互換性のある技術を使って、200mmウエハー上にグラフェンICを製造した。

IBMの研究チームは、2GHzの高周波信号を扱える周波数てい倍器を集積したチップを、200mmウエハーを使って製造することに成功した。この製造技術は、シリコン材料を用いる一般的なCMOSチップの製造プロセスと互換性があるという。この成果について、2011年12月5〜7日に米国ワシントンD.C.で開催される半導体素子の国際学会「2011 IEEE International Electron Devices Meeting(IEDM)」で発表する†1)。

グラフェンは、カーボンナノチューブと同様に、炭素原子が六角形の「ハニカム(蜂の巣)格子」を形成したシート状の炭素材料である。グラフェンでは電界効果のみならず、バリスティック伝導(電子が不純物によって散乱することなく、結晶内を通過する現象)も発生し、電子移動度がシリコンに比べて最小でも40倍と高い。電流密度が高く、電子の移動度と飽和速度が高いといった優れた特性を備えていることから、高性能の電子回路を実現可能な材料技術として期待されている。一方で工業的な量産性に着目すると、炭素は取り扱いが難しく、ウエハー処理工程で問題が起きやすい。そのためこれまでに報告されている成果は、単一のトランジスタ素子や、簡単な集積回路(IC)にとどまっていた。

IEDMが公表した論文の概要によれば、IBMは200mm口径のウエハーに、CMOS互換の製造プロセスでグラフェンICを作り込むことに成功した(図1、図2)。グラフェンICを商用化に一歩近づける成果だといえる。

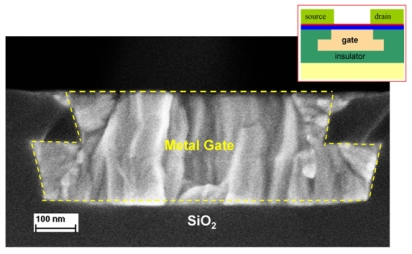

ウエハーの断面の電子顕微鏡写真 化学機械研磨(Chemical Mechanical Planarization:CMP)処理後のウエハーの断面を電子顕微鏡写真で撮影した。逆T字型のゲート構造が見て取れる。

ウエハーの断面の電子顕微鏡写真 化学機械研磨(Chemical Mechanical Planarization:CMP)処理後のウエハーの断面を電子顕微鏡写真で撮影した。逆T字型のゲート構造が見て取れる。グラフェンの表面は化学的に不活性であり、ゲート電極を絶縁するための誘電体層を作り込むことが難しかった。そこでIBMは、IEDMが公表した概要によると、一般的な製造プロセスの順序を反転させるという手法を採用した。先にゲート構造をシリコンウエハーの上に形成しておき、その後で、化学気相成長法(Chemical Vapor Deposition:CVD)を使って作成した複数のグラフェン層をそのシリコンに転写するというものだ。グラフェン領域の境界を定めてから、ソースとドレインのコンタクトを作成し、FET構造を完成させるという手順である。

今回IBMが試作した周波数てい倍器ICは、複数のFETと高周波要の受動部品を組み合わせて集積したもので、IEDMが発表しているデータによれば、2GHzにおいて約−25dBの変換利得が得られているという。

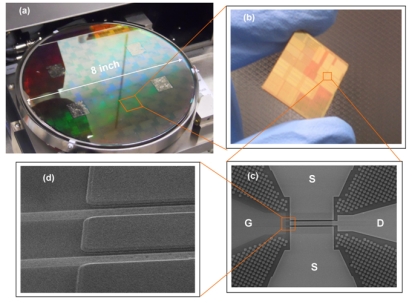

グラフェンFETを作り込んだウエハー (a)は、グラフェンFETを作り込んだ200mm口径のウエハー。(b)は、そのウエハーから切り出したチップ。(c)は、チップ上に集積されているFET素子のSEM(走査型電子顕微鏡)画像。(d)は、FET素子の拡大画像で、2フィンガー構造の埋め込みゲート部分である。CVDで形成しておいたグラフェン層をシリコンに転写する処理を除けば、他の全工程は従来の200mmウエハーラインで処理できるという。

グラフェンFETを作り込んだウエハー (a)は、グラフェンFETを作り込んだ200mm口径のウエハー。(b)は、そのウエハーから切り出したチップ。(c)は、チップ上に集積されているFET素子のSEM(走査型電子顕微鏡)画像。(d)は、FET素子の拡大画像で、2フィンガー構造の埋め込みゲート部分である。CVDで形成しておいたグラフェン層をシリコンに転写する処理を除けば、他の全工程は従来の200mmウエハーラインで処理できるという。関連記事

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増