大規模半導体設計の最新状況を探る ―― CDNLive! Japan 2011リポート:EDAツール(1/2 ページ)

EADツール大手ベンダーの日本ケイデンス・デザイン・システムズ社が10月13日に横浜で開催した顧客向け技術講演会から、米国本社の幹部による基調講演の模様をリポートする。また、併設の展示会で目を引いた、パートナー企業のシリコンファウンドリ事業の展示を紹介する。

半導体設計ツール(EDAツール)の大手ベンダー米国Cadence Design Systemsの日本法人である日本ケイデンス・デザイン・システムズ社(以降は日本ケイデンス)は、顧客向け技術講演会「CDNLive! Japan 2011」を2011年10月13日に横浜のパンパシフィック横浜ベイホテル東急で開催した。

日本ケイデンスは過去、毎年7月に2日間にわたって東京の明治記念館で顧客向けの技術講演会を開催してきた。講演内容は同社の考える半導体設計の将来像や、同社の半導体設計ツール(EDAツール)製品の解説、ユーザーによる半導体設計事例などである。

今年は東日本大震災の影響もあってか、日程は1日間に短縮され、開催時期は秋に変更された。例年の2日間にわたる大規模な講演会に比べると、やや寂しくなったとの印象は否めない。ただし、開催時期が10月になったのは来場者にとって好評だった。過去の7月開催では、相当に厳しい暑さの中を会場へと足を運ぶ羽目になることが多かったからだ。

当日のスケジュールは、始めに全体講演セッションである基調講演セッションが設けられ、その後、3〜4カ所の会場に分かれて一般講演セッションが開催されるというものである。各講演会場を行き来する広めの廊下には、テーブルトップ形式の展示会が併設された。

本リポートでは基調講演セッション(図1)の概要と、併設の展示会の様子をお届けする。

基調講演セッションでは、米国Cadenceでワールドワイド・フィールド・オペレーション担当シニアバイス・プレジデントを務めるCharlie Huang氏が、「Realizing EDA360 −次なるチャレンジに向けて−」と題して講演した。

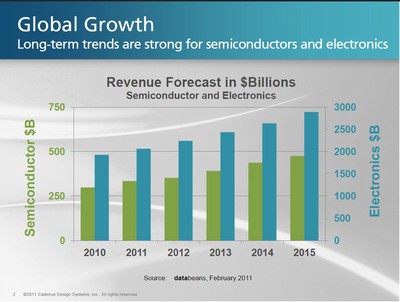

Huang氏は始めに、世界の電子産業と半導体産業の市場規模を示した。今年(2011年)の市場規模は電子産業が約2兆米ドル、半導体産業が約3000億米ドルと見込まれている(図2)。これが2015年には、電子産業が3兆米ドルに近付き、半導体産業が5,000億ドルに近付く。

図2 半導体産業と電子産業の市場規模の推移 緑色が半導体産業、青色が電子産業の市場規模。単位はともに10億米ドル。データの出所は、米国の市場調査会社であるDatabeansが2011年2月に発表したリポートである。

図2 半導体産業と電子産業の市場規模の推移 緑色が半導体産業、青色が電子産業の市場規模。単位はともに10億米ドル。データの出所は、米国の市場調査会社であるDatabeansが2011年2月に発表したリポートである。中期的には堅調な成長が見込まれるものの、直近ではマクロ経済の景気減速が明確になり、厳しい状況に直面している。四半期ベースの経済成長率(GDP)で見ると米国は2010年12月時点の3.3%成長から四半期ごとに下がり続け、直近の2011年9月時点では1.4%成長まで低下した。欧州は2010年12月時点から2011年9月時点までが1.6%成長〜2.2%成長と低い成長率が続いており、直近の2011年9月時点が1.6%成長と最も低い数値になった。高成長を続ける新興国市場(エマージング市場)は2010年12月時点から5.9%、6.0%、6.1%と伸びてきたものの、2011年9月時点では5.7%成長と一服感が見える。

電子産業の成長を中期的にけん引するのは大きなイノベーションであり、それはPCから、“ポストPC”へとシフトする、とHuang氏は述べた。ポストPCのイノベーションをけん引するのは新たなアプリケーション、それも数多くのアプリケーションを搭載したシステムだとする。その一例として、数多くのアプリケーションが動作する腕時計型の無線通信端末を挙げていた。

システム開発基盤の変化と提携の増加

アプリケーションがイノベーションをけん引することで、電子産業は四つの影響を受けるとHuan氏は続けた。

- 新しい開発プラットフォーム(New development platform)が必要になる

- IPがコアを超えた広がりを持つようになる(IP expanding beyond cores)

- 提携や協調などのコラボレーションが増える(Incresing collaboration)

- EDAツールが変化し続ける(EDA is changing)

システム開発企業はハードウェアやソフトウェアなどではなく、アプリケーションでシステムの差異化を図るようになる。このために半導体ベンダーは、アプリケーションに対応したソフトウェアとハードウェアのプラットフォームをシステム開発企業に提供しなければならなくなる。これが新しい開発プラットフォーム(New development platform)だ。

開発プラットフォームの構成要素であるIP(ソフトウェアIPとハードウェアIP)は、開発ターゲットとなるアプリケーションの実現に適したものになる。それは演算処理、インタフェース、記憶といったコア(ハードマクロ)ではなく、ソフトウェアIPとハードウェアIPが結びついた、より大きな概念のIPである。

そうなると、IPベンダー、EDAツールベンダー、ソフトウェアベンダー、システム開発企業、半導体テストベンダー、半導体パッケージベンダー、半導体ファウンドリ、標準化団体などが連携することが、開発プラットフォームの構築に必須となる。以前に比べると関係するベンダーが増え、共同開発や提携、協調作業などが活発になっていく。

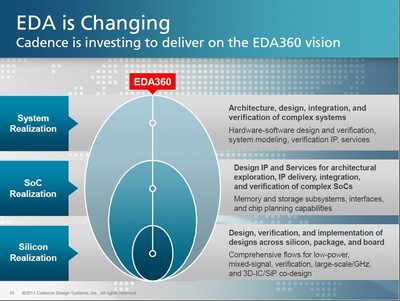

このような状況認識の下、EDAツールベンダーであるケイデンスは、顧客に提供する製品の姿を新しい時代に対応したものに変えつつある。そのコンセプトが「EDA360」であり、ケイデンスが2010年に提唱したものだ。

「EDA360」を実現するツール(ソリューション)は、大きく3つに分けられる。システム開発ソリューション(System Realization)、SoC(System on a Chip)開発ソリューション(SoC Realization)、シリコン開発ソリューション(Silicon Realization)である(図3)。

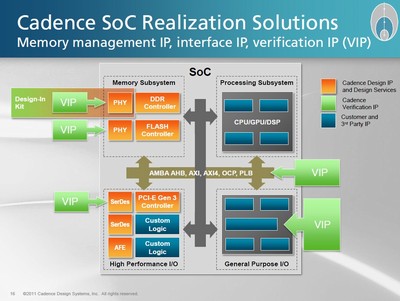

例えばSoC開発では、複数のメモリインタフェースに対応しなければならない、標準仕様が絶えず変化する、高性能I/Oを設計できる熟練の技術者が必要、複数のサブシステム(回路ブロック)を接続する複数のインタフェースを検証しなければならない、といった課題がある。これに対してCadenceでは、複数のメモリに対応したコントローラIP、高速I/Oに対応したSerDes IPやアナログフロントエンドIPのほか、インタフェースやサブシステムなどの検証を支援する検証用IP(VIP)を提供している(図4)。

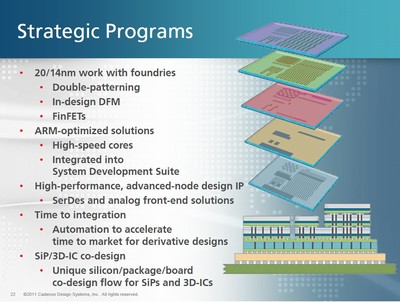

講演の最後には、Cadenceが開発中のプログラムをまとめて示した(図5)。20nm/14nmの次世代デバイス・プロセス技術に向けてファウンドリと共同で開発を進めている他、ARMアーキテクチャに最適化したコアを開発し、開発環境に組み込もうとしている。また、SiP(System in Package)や3次元ICなどの新しいパッケージング技術に対応し、シリコンとパッケージ、実装基板(プリント基板)をまとめて扱える協調設計ツールを開発中である。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

図1 基調講演セッションの会場風景(講演開始直前に撮影) パンパシフィック横浜ベイホテル東急の地下宴会場フロアが使われた。

図1 基調講演セッションの会場風景(講演開始直前に撮影) パンパシフィック横浜ベイホテル東急の地下宴会場フロアが使われた。