世界人口に相当するトランジスタが45mm角に、Xilinxが最大規模のFPGA出荷:プログラマブルロジック FPGA(1/2 ページ)

単一のパッケージに複数のFPGAチップを納める独自技術を適用することで実現した最大規模品である。ロジック規模はASICゲート換算で2000万〜4000万ゲートに相当し、トランジスタ数は68億個に達する。出荷を開始したのはエンジニアリングサンプル品で、量産品の出荷は2012年第4四半期の予定だ。

FPGA大手ベンダーのXilinx(ザイリンクス)は、ロジックセルの規模が200万個と極めて大きいFPGAの出荷を始めたと発表した。28nm世代の半導体プロセス技術で製造する最先端FPGA「Xilinx 7シリーズ」のハイエンドファミリで、最大規模品となる「Virtex-7 2000T」である。

同社は1年前の2010年10月に、単一のパッケージに複数のFPGAチップ(ダイ)を納める独自技術「スタックド シリコン インターコネクト」を適用してこの最大規模品の開発を進めていると発表しており(参考記事)、今回はその製品が実際に出荷されたことを明らかにした。「2011年9月27日に、ある顧客企業にエンジニアリングサンプル品を出荷した。他にも、日本企業を含む数多くの顧客から発注を受けており、それらの出荷準備を進めているところだ」(Xilinxで製品開発担当バイス プレジデントを務めるSteve Douglass氏)という(図1)。今後、品質認証を経て、2012年の第4四半期(10〜12月)に量産出荷を始める予定だ。

図1 XilinxのSteve Douglass氏 製品開発担当バイス プレジデントを務めている。日本法人のザイリンクスが今回の発表に当たって国内の報道機関向けに開催した説明会に登壇した。右手に掲げているのがVirtex-7 2000Tのエンジニアリングサンプル品である。

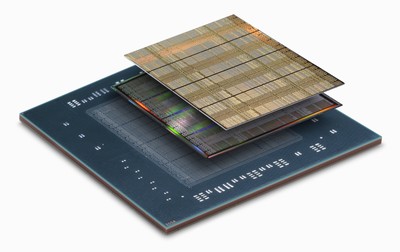

図1 XilinxのSteve Douglass氏 製品開発担当バイス プレジデントを務めている。日本法人のザイリンクスが今回の発表に当たって国内の報道機関向けに開催した説明会に登壇した。右手に掲げているのがVirtex-7 2000Tのエンジニアリングサンプル品である。この最大規模品は、45mm×45mmのパッケージの中に、50万個のロジックセルを集積したFPGAダイを4枚内蔵し、シリコン材料を使った支持基板(インターポーザ)を介して相互に接続している(図2)。これにより200万個のロジックセルを実現した。このロジックセル数をASICのゲート数に換算すると、2000万〜4000万ゲートに達するという。「この単一のパッケージの中に、実に68億個ものトランジスタが内蔵されている。これは、世界の人口に相当する数だ」(同氏)。

ロジック規模・処理性能・消費電力、「全てで競合を大きくしのぐ」

同社は今回の発表に当たり、スタックド シリコン インターコネクト技術を適用した最大規模品の利点をあらためて説明した。第1の利点は、単一ダイのFPGAでは実現できない規模のロジックセルを提供できることだ。「半導体の製造プロセスは、世代ごとにレチクル(フォトマスク)のサイズに上限があり、物理的に製造可能なダイサイズがそれで決まってしまう。つまり単一ダイで実現できるロジック規模には限界がある。スタックド シリコン インターコネクト技術を使えば、単一パッケージ内でその限界を超えるロジック規模を提供することが可能だ。「競合他社が28nm世代で提供する最大規模品は単一のダイを用いている。それを2個使っても、ロジックセル換算で190万個相当の規模しか得られない」(同氏)と主張する。

第2の利点は、複数のFPGAダイをまとめることで高い処理性能を確保できることだ。例えばVirtex-7 2000Tでは、4枚のFPGAダイの合計で2160個のDSPブロックを搭載しており、700MHzで駆動すれば単一パッケージで1.5TMACSの積和演算性能を発揮する。「競合他社の単一ダイの最大規模品は、パッケージを4個組み合わせても1.2TMACSにとどまる」(同氏)と説明する。

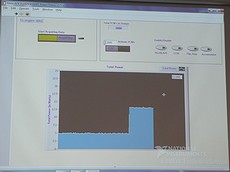

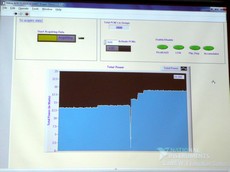

第3の利点は、消費電力を低く抑えられることだ。プリント基板上で複数のFPGAを組み合わせる手法では、FPGA間の接続に消費電力の大きなインタフェースが必要になる。これに対しスタックド シリコン インターコネクトでは、パッケージ内部でFPGAダイ同士をつなぐインタフェースは、ダイ内部でノードとノードを接続するインタフェースとまったく同じ回路構成だという。つまり、ダイ間で信号を入出力しても、消費電力はダイ内で信号をやりとりする場合とほとんど変わらない程度に抑えられる。さらに高性能ながら低消費電力を特徴とする半導体プロセスを選択したことと相まって、「競合他社の最大規模品をプリント基板上で4個組み合わせて実装する回路で112Wを消費するところ、Virtex-7 2000Tdなら19Wに抑えられる」(同氏)という(図3、図4)。

報道機関向けの説明会では、Virtex-7 2000Tの消費電力を実測するデモの様子も見せた。ロジックセル領域に3600個の8ビットプロセッサブロックの他、複数の周辺回路ブロックを実装した状態で、消費電力をリアルタイムに測定しながら、各ブロックを稼働させて消費電力が増加していく様子を観測している。200万個のロジックセルの84%を専有する規模のデザインだという。図3(左)は、全ての回路ブロックが停止している状態から、途中で3600個の8ビットプロセッサブロックを全てオンに切り替えて、100MHzで動作させた。消費電力は、全停止状態で5W、全動作状態でも12.5W程度だ。図4(右)は、周辺回路ブロックも全てオンにした状態で、それでも約19Wに抑えられていることが読み取れる。

報道機関向けの説明会では、Virtex-7 2000Tの消費電力を実測するデモの様子も見せた。ロジックセル領域に3600個の8ビットプロセッサブロックの他、複数の周辺回路ブロックを実装した状態で、消費電力をリアルタイムに測定しながら、各ブロックを稼働させて消費電力が増加していく様子を観測している。200万個のロジックセルの84%を専有する規模のデザインだという。図3(左)は、全ての回路ブロックが停止している状態から、途中で3600個の8ビットプロセッサブロックを全てオンに切り替えて、100MHzで動作させた。消費電力は、全停止状態で5W、全動作状態でも12.5W程度だ。図4(右)は、周辺回路ブロックも全てオンにした状態で、それでも約19Wに抑えられていることが読み取れる。Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- パワー半導体再編が本格化 ローム・東芝・三菱電機が協議開始へ

- 「究極の半導体」ダイヤモンドを社会へ 動態展示も実現の早大発新興

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- JDIが鳥取工場を売却、車載用液晶パネル拠点

- 「世界2位」は実現するか、ローム、東芝、三菱電機とデンソーの選択は

- シャープ新社長は海外事業出身 鴻海と連携で「新たな成長ステージへ」

- ソニー、新会社「BRAVIA」にテレビ事業を承継 企業価値1028億円

- もはや半導体メーカーの域を超えた NVIDIA最新エッジ機器を分解

- 魚津はTower、砺波はNuvotonに TPSCo事業の再編を発表