「ソニーの裏面照射型CMOSセンサーにも採用」、酸化膜接合の新技術のインパクトとは!?:プロセス技術

米国の研究都市Research Triangle Park発のベンチャー、Ziptronixの独自の酸化膜接合技術を使えば、裏面照射型CMOSセンサーを高画素化できる。半導体の高集積化の手法として注目が集まっている3次元積層技術にも適用できるという。

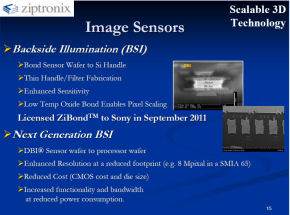

米国の研究都市Research Triangle Park発のベンチャー企業であるZiptronix(ジプトロニクス)が、独自の酸化膜接合技術の売り込みを本格化させている。2009年にハイエンドのイメージセンサーを手掛けるRaytheon Vision Systemsに初めてライセンス供与した後、2011年には裏面照射型イメージセンサー向け酸化膜接合技術のライセンス契約をソニーと締結した。さらに、2011年末までに1件、2012年第2四半期末までに2件のライセンス契約を締結できる見通しだという。

同社のPresident兼CEOのDaniel L. Donabedian氏は、「当社の接合技術は、次世代の裏面照射型イメージセンサーやRFフロントエンドモジュール、メモリチップやプロセッシングチップを3次元に積層したSiPといったさまざまな用途で活躍する」と語る。

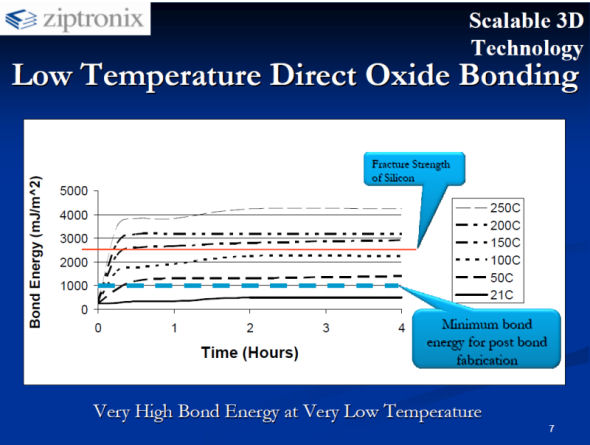

低温で高い接合強度

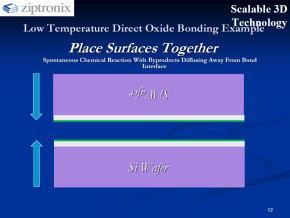

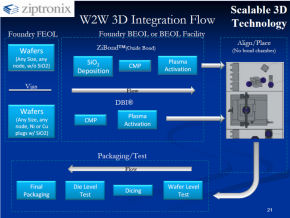

Ziptronixが提供しているのは、「ZiBond」と「DBI」と呼ぶ2つの酸化膜接合技術である。両者の違いは、接合する2つのチップの電気的な接続(インターコネクト)に対応しているかどうかにある。ZiBondはインターコネクトが無い機械的な接合のみを想定したプロセス技術で、一方のDBIはインターコネクトがある場合となっている。ZiBondおよびDBIの最大の特徴は、低温環境で高い接合強度が得られることである。しかも同社は、既存の製造装置をそのまま使えると主張する。

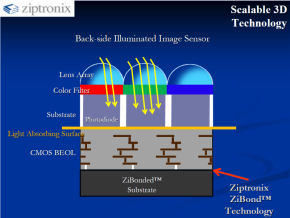

裏面照射型イメージセンサーを例に挙げると、製造時に支持基板とCMOSチップを接合する必要がある。この工程に、同社の酸化膜接合技術が使える。低温環境下であるため、熱膨張によるひずみが発生しにくく、同一チップ面積で比較したとき、イメージセンサーの画素数を高められると主張する。チップの接合に接着剤を使った場合、高温処理が必要で、熱膨張によってチップにひずみが生まれてしまうという。

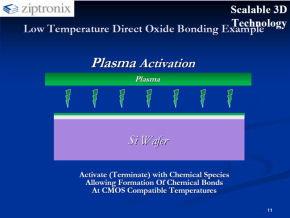

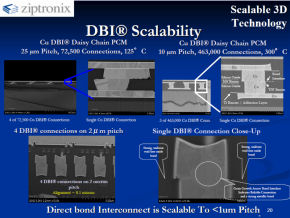

接合の原理については、以下のように説明した。まず、チップにSi(シリコン)の酸化膜を積層し、CMP(化学的機械研磨)処理を施す。その後、プラズマ処理によって酸化膜界面を活性化させ、界面を活性化させたチップ同士を接触させることで、両者を接合させる。「シンプルで明解な技術だ」(Donabedian氏)。接合による純抵抗の増加や、1GHzを超えるような高周波信号を流したときの損失もほとんどないと主張する。DBIは現在、電極間隔が2μmまで対応しており、将来的には1μmまで狭められるという。

“積層”が未来のICの姿

Ziptronixは10年以上前から、酸化膜接合技術の開発を進めてきたが、最近になって急速に需要が高まっているという。その要因は、微細化の限界が見えてきたことにある。

現在量産されている最先端の製造プロセスは、20nmクラス(20nm〜29nm)である(関連記事)。半導体ファウンダリ最大手のTSMC(Taiwan Semiconductor Manufacturing Company)は「FinFET(立体構造トランジスタ)を利用すれば、7nmノードまで微細化されるだろう」と説明しているものの、導入コストの観点で今後の微細化はそう簡単には進みそうにない(関連記事)。

このような背景があり、半導体の高集積化/多機能化をさらに進める手法として、3次元積層に注目が集まっている(関連記事)。機能の異なるチップを積層することで、微細化を進めずとも、回路規模を増やせる。「これまで3次元積層という新技術の導入に慎重な企業が多かったが、そうも言っていられない状況だ。研究開発は、急ピッチで進んでいる」(Donabedian氏)。

複数のチップを積層するには、バンプやインターポーザーを介してチップを電気的に接続する方法がある。Ziptronixが提案するのは、インターコネクトを確保しつつ、チップ間を直接接合する方法である。「現状の3次元積層技術は、チップ間にすき間ができてしまうためストレスにそれほど強くなかったり、余分な厚みが生まれてしまうといった課題がある」(同氏)という。

関連記事

画素が1.12μmと小さい裏面照射CMOSセンサーを東芝開発、スマホに年内量産

画素が1.12μmと小さい裏面照射CMOSセンサーを東芝開発、スマホに年内量産

東芝はデジタルカメラやスマートフォン、タブレットPCなどの高画質センサーとして今後、裏面照射型が主流になると見込む。 ザイリンクス、28nm世代の次期FPGAで3次元パッケージを採用

ザイリンクス、28nm世代の次期FPGAで3次元パッケージを採用

ザイリンクスは、28nm世代の半導体プロセス技術で製造する次世代FPGA「Xilinx 7シリーズ」に3次元パッケージ技術を採用したと発表した。 3次元チップ設計における5つの課題、IBMの研究者が語る

3次元チップ設計における5つの課題、IBMの研究者が語る

昨今の半導体チップ設計の世界で、最も挑戦的な課題は3次元構造を採るチップ設計だろう。半導体チップ・メーカーは現在、既存の半導体チップを積層する手法を模索している。- 半導体メーカー6社が、SEMATECHのシリコン貫通電極の研究プログラムに参加

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

ZiptronixのPresident兼CEOのDaniel L. Donabedian氏(写真左)と、同社CTO兼R&D部門のVice PresidentであるPaul Enquist氏(写真右)

ZiptronixのPresident兼CEOのDaniel L. Donabedian氏(写真左)と、同社CTO兼R&D部門のVice PresidentであるPaul Enquist氏(写真右)