電源から電力を取り出す逆転の発想とは?:パワー半導体(1/2 ページ)

サーバ用電源では効率向上が強く求められている。富士通研究所は電源内部で発生する性質の異なった2種類の損失を防ぐために、それぞれ新規開発の技術を適用、94.8%の最高効率を実現した。特にトランジスタ内で生じるスイッチング損失を、一種の「回生回路」で再利用する取り組みが新しい。さまざまな機器の電源に応用できる。

電源の改良は、家電製品や組み込み機器、IT機器などの消費電力引き下げに欠かせない。電源の機能は100Vまたは200Vの交流を、数〜数十Vの安定した直流に変換することだ。「変換」という言葉が暗示するように、100%の効率は達成できない。変換できなかった電力は損失となり、発熱につながる。発熱による過熱を防ぐためには、電源に冷却装置を取り付ければならず、システム全体としての消費電力はさらに増えてしまう。従って、電源を開発する際には効率向上について常に考えなければならない。

コスト低減や小型化、信頼性向上などを電源の開発目標とした場合にも、いかに損失を低く抑えるかがカギとなる。損失が低ければ、熱対策コストが減り、例え電源を小型化したとしても熱密度が高くなりにくい。さらに動作温度が下がれば、信頼性は高まる。

2種類の損失が別々に起こる

どうすれば電源の損失を低く抑え、効率を高められるのだろうか。電源内部の損失の要因は大きく、2つに分けられる。「デッドタイム損失」と「スイッチング損失」だ。

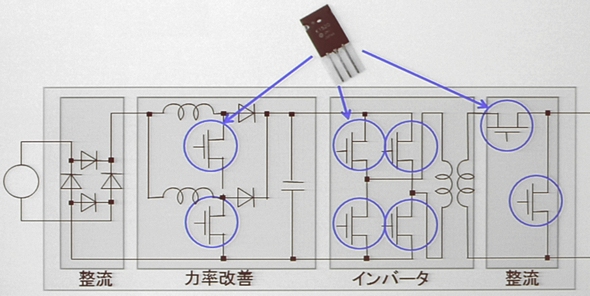

図1 電源の一般的な内部構成 左端の交流電流源から入力を得、整流、力率改善をへてインバータを通過、整流後、直流(例えば12V)を出力する。内部に多数のスイッチ(トランジスタ)が含まれていることが分かる。以下、出典:富士通研究所

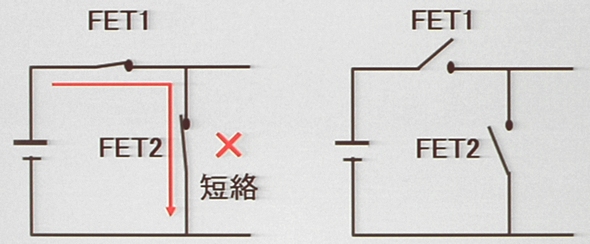

図1 電源の一般的な内部構成 左端の交流電流源から入力を得、整流、力率改善をへてインバータを通過、整流後、直流(例えば12V)を出力する。内部に多数のスイッチ(トランジスタ)が含まれていることが分かる。以下、出典:富士通研究所デッドタイム損失は、電源がスイッチの固まりであることに由来する(図1)。電源内部では多数のスイッチが協働してオン/オフを繰り返し、電圧を変換している。このとき2つのスイッチが同時にオンになってはならない。2つのスイッチが同時にオンになると短絡(ショート)が起こり、事故につながるからだ。

しかし、スイッチのオン/オフ切り替えにはある程度の時間がかかるため、2つのスイッチが同時にオンにならないようにすると、どうしても同時にオフになる瞬間が生じる(図2)。これが損失につながる。このような損失をデッドタイム損失と呼ぶ。

デッドタイム損失と並んで影響が大きいのが抵抗損失とスイッチング損失だ。スイッチとしての機能を果たすトランジスタ「FET」(Field Effect Transistor)には電流が流れる。FETには必ず抵抗成分があり、ここで損失が起こる。これが抵抗損失だ。この損失を減らすには抵抗の小さなFETを選べばよい。

しかし、低抵抗のFETを選ぶと、今度はスイッチング損失が増えてしまう。抵抗を小さくするためにFETを大型化すると、FETが容量の大きなコンデンサとして働き、スイッチがオンになった瞬間に電流が漏れ出して熱に変わるからだ。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

最高効率94.8%

最高効率94.8% 図2 スイッチング動作とショートの関係 2つのスイッチが同時にオンになることを避けると、どうしても同時にオフになる瞬間が生じる

図2 スイッチング動作とショートの関係 2つのスイッチが同時にオンになることを避けると、どうしても同時にオフになる瞬間が生じる