電源から電力を取り出す逆転の発想とは?:パワー半導体(2/2 ページ)

2種類の損失を抑えて高効率に

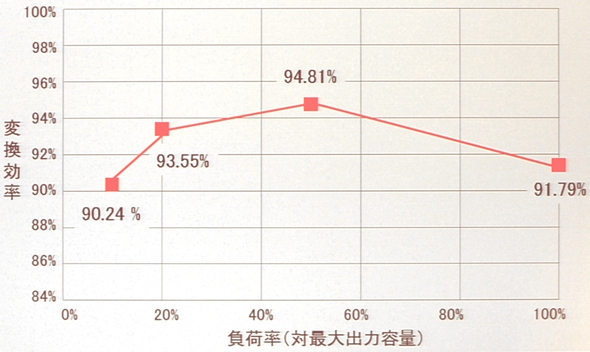

富士通研究所はデッドタイム損失と、スイッチング損失の両方に対策を施したサーバ向け電源を試作した(図3)。容量2.3kWの大容量電源*1)であり、変換効率は世界最高となる94.8%を達成したと主張する(図4)。

*1) 富士通によれば、例えば64個のCPU(256コア)を内蔵するUNIXサーバ「SPARC Enterprise M9000」の消費電力は40.4kW、36個のCPU(128コア)を搭載するブレードサーバ「PRIMERGY BX900」の消費電力は12.9kWであるという。これらの電力をまかなうには、試作した電源を複数組み合わせて使う必要がある。

図3 試作したサーバ用電源 12V出力で容量は2.3kWだ。サイズの比較のため左下に硬貨を置いた。今回開発した技術を搭載した電源を2014年にサーバ製品へ搭載することを目指して、さらなる高効率化と、信頼性や安全性の評価を続けるという。

図3 試作したサーバ用電源 12V出力で容量は2.3kWだ。サイズの比較のため左下に硬貨を置いた。今回開発した技術を搭載した電源を2014年にサーバ製品へ搭載することを目指して、さらなる高効率化と、信頼性や安全性の評価を続けるという。 図4 試作したサーバ用電源の変換効率 最大出力容量に対する負荷率が50%のとき、最高変換効率94.81%を達成した。低負荷領域ではスイッチング損失の低減が効き、高負荷領域ではデッドタイム損失対策が有効だという。出典:富士通研究所

図4 試作したサーバ用電源の変換効率 最大出力容量に対する負荷率が50%のとき、最高変換効率94.81%を達成した。低負荷領域ではスイッチング損失の低減が効き、高負荷領域ではデッドタイム損失対策が有効だという。出典:富士通研究所デジタル制御と新回路で対応

同社はどのように高効率を実現したのだろうか。デッドタイム損失に対してはデジタル制御技術を利用して改善し、スイッチング損失対策としては、外部にエネルギー再利用回路を追加した。

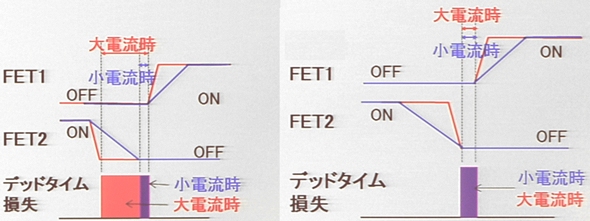

FETの動作は、流す電流の大きさによって変わる。大電流ではスイッチの速度が高まり、小電流では遅くなる。安全を見込んで小電流時のFETの速度に切り替えタイミングを合わせると、大電流を流したときにデッドタイムが長くなってしまう。かといって、大電流に合わせ込むと、小電流時に短絡が起きる。サーバ用の電源は常に負荷が変化するため、安全を見込んでデッドタイムを長くとる必要がある。

なんらかの手法でデッドタイムを短くできないだろうか。同社の対策は電流値をリアルタイムに測定して、FETのオフ期間を常に最短に制御することだ(図5)。一種のソフトスイッチング技術である。これでデッドタイム損失を抑えることができた。「オフ期間は100ns〜1μs程度の長さだ。サーバが搭載するボードからの消費電流の変動(電源から見た負荷変動)に応答するには、数ms以内でスイッチングのタイミングを変えることができればよい。マイコンを搭載し、あらかじめ登録した値テーブルを参照することで、高速応答を実現した」(富士通研究所ITシステム研究所サーバテクロノジ研究部の米澤遊氏)。

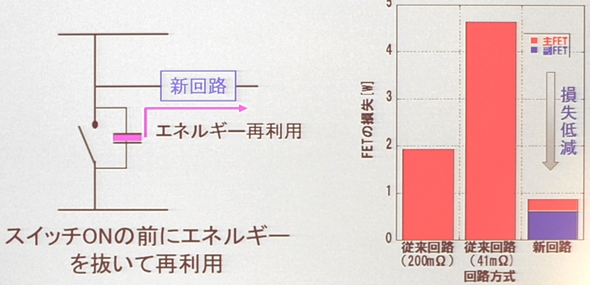

スイッチング損失を抑える手法は一種のエネルギーハーベスティング技術ともいえるだろう。スイッチオフ時にFET内部にたまった電荷を回収する回路を新規開発し、損失を抑えた(図6)*2)。「FETの低い抵抗値はそのままに、スイッチング損失を大幅に低減できている」(米澤氏)。つまりFETの抵抗損失とスイッチング損失を同時に低減することに成功したことになる。新回路はFETやトランスなどのディスクリート部品で構成し、もともとのFETと同程度の面積に実装できたという。

*2) 英ブリストル市で2012年3月27〜29日に開催された学会「Power Electronics Machines & Drives Conference 2012」で発表した。

図6 スイッチング損失を低減する手法 FETの外部に電荷を回収する新回路を追加した(左)。従来のFETでは抵抗が200mΩの場合約2Wのスイッチング損失がFETで生じている。41mΩの場合は約4.5Wのスイッチング損失が起こっていたが、これを1W以下に低減できた(右)。なお、新回路にもFETが含まれているため、その損失分を青で示している。青い損失を追加しても従来より低減できている。

図6 スイッチング損失を低減する手法 FETの外部に電荷を回収する新回路を追加した(左)。従来のFETでは抵抗が200mΩの場合約2Wのスイッチング損失がFETで生じている。41mΩの場合は約4.5Wのスイッチング損失が起こっていたが、これを1W以下に低減できた(右)。なお、新回路にもFETが含まれているため、その損失分を青で示している。青い損失を追加しても従来より低減できている。関連記事

CPUの廃熱でデータセンターを冷やす、空調を20%節電する技術を富士通開発

CPUの廃熱でデータセンターを冷やす、空調を20%節電する技術を富士通開発

水冷式の温排水の熱を使って冷水を製造 サーバからファンを外すとよく冷える、富士通が消費電力40%低減に成功

サーバからファンを外すとよく冷える、富士通が消費電力40%低減に成功

外気を直接取り込み、独立したファンで吹きかける デジタル制御電源を学ぶ(1) デジタル電源は何がどう「デジタル」なのか

デジタル制御電源を学ぶ(1) デジタル電源は何がどう「デジタル」なのか

安定した電圧を出力するために常に制御が必要

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

図5 デッドタイム損失の低減手法 電流値を測定して、常にデッドタイムを短くする仕組みを取り入れた。具体的には大電流時のデッドタイムを小電流時のデットタイムまで短縮した。

図5 デッドタイム損失の低減手法 電流値を測定して、常にデッドタイムを短くする仕組みを取り入れた。具体的には大電流時のデッドタイムを小電流時のデットタイムまで短縮した。