DRAM各社のプロセスを比較、さらなる微細化は可能か:メモリ/ストレージ技術(1/2 ページ)

DRAMは、幾度となく「微細化はもう限界」だと言われてきた。だが、メーカー各社は2Xnmや1Xnm世代のDRAMの実現に向けて試行錯誤を繰り返し、成果を出し始めているという。

かつて、DRAMのメモリーセルの微細化は30nmで壁に突き当たると予想されていた。だが、大手DRAMメーカー各社が現在適用している最先端のDRAMセル技術を詳細に分析すると、2Xnmや1Xnmノードの実現に向けて技術が進歩していることが分かる。

TechInsightsは、大手DRAMメーカーのSDRAMのセルアレイ構造を分析し、各社が採用するプロセス技術やデバイス構造に関する報告書を発表した。同報告書は、Samsung ElectronicsやSK-Hynix、Micron Technology/Nanya Technology、エルピーダメモリが量産する、3Xnmプロセス技術を適用したSDRAMを対象とし、「DRAMはさらに微細化できる」と結論づけている。ただし、この結論は、埋め込みワード線(b-WL)やフィン型アクセストランジスタなどの技術を利用することを前提としたものである。

DRAMのセル構造に現在適用されている3Xnm台前半のノードで、プロセス技術の統合に最も重要となるのは、アクセスMOSFETのチャネル長を効率的に増やすことと、DRAMのセルアレイのストレージキャパシタ領域を微細化することだ。

3X/2Xnmのアクセストランジスタの微細化を実現する鍵となるのは、サドル型(またはバルクフィン型)の埋め込みメタルワード線技術を適用したチャネル構成や、閾(しきい)値電圧の的確な制御、リーク電流を極限まで低く抑えることなどである。トランジスタのチャネル幅とチャネル長が大きいほど、短チャネル効果や、オン電流がより高くなった時の影響を受けにくくなる。

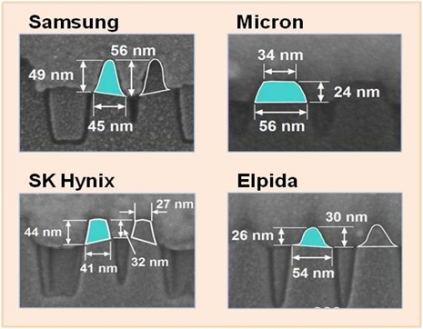

現在、DRAMメーカー4社は、ほぼ同様の工程で、リセス型トランジスタやフィン型トランジスタを製造している。

チャネル長が最大なのはエルピーダ

図は、各メーカーのフィン型トランジスタの形状である。MicronとSK-Hynixは、台形のバルクフィン型を採用している。4社のトランジスタのチャネル幅とチャネル長を総合的に比較すると、Micron/Nanyaのセルトランジスタはチャネル幅が最大で、エルピーダのセルトランジスタはチャネル長が最大である。Samsungは埋め込みワード線のゲート材料に、他の3社が採用していない、タングステンより抵抗の高いTiN(スズ)金属ゲートを採用している。ビット線層に関しては、4社ともタングステンベースの材料を使っている。ただし、タングステン層とポリSi(シリコン)層の間のバリア材料は、各メーカーで異なる材料が使われている。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

DRAMメーカー4社のフィン型トランジスタの構造

DRAMメーカー4社のフィン型トランジスタの構造