富士通研究所、従来比3倍の3000原子規模ナノデバイスのシミュレーションに成功:新技術

富士通研究所は、ナノデバイスの電気特性をシミュレーションする技術として従来比3倍となる3000原子規模のナノデバイスに対応する技術を開発したと発表した。この技術により、新材料を用いるなどした次世代デバイスの開発期間/コストを削減できるという。

富士通研究所は2014年1月14日、3000個程度の原子で構成される規模のナノデバイスの電気特性をシミュレーションする技術を開発したと発表した。スパコンを用いた大規模並列化技術と計算に利用するメモリ容量を削減する技術などで、従来よりも3倍となる3000原子規模の電気特性シミュレーションを可能にしたという。この技術により、新材料を用いるなどしたナノデバイスを試作する前に、より正確に電気特性を把握できる。

システムLSIなどナノデバイスは、微細化がより技術的に難しくなり、新しい材料や新しい構造を用いた次世代デバイス開発が活発に行われている。ただ、次世代デバイスの開発は、電気特性を測定、評価するために試作実験を繰り返す必要があり開発期間/コストの増大を招いた。一方で、新型デバイスの電気特性を計算機上で正確にシミュレーションできれば、試作実験を行う回数を大幅に減らすことが可能になり、開発期間/コストの削減が期待できる。

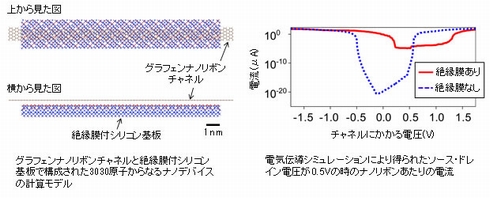

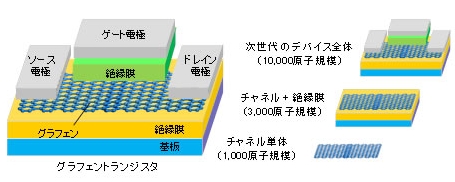

ナノデバイスの電気特性を正確にシミュレーションするには、1つ1つの原子の振る舞いを正確に計算する「第一原理計算」によるシミュレーションが有効とされている。しかし第一原理計算は、膨大な計算が必要なため、電気特性予測に適用する場合、「1000原子規模にとどまっていた」(富士通研究所)。そのため、シミュレーションできる規模も「電子の通り道であるチャネル部分だけの計算が可能であり、電気特性に大きな影響を及ぼすと考えられる隣接する電極や絶縁膜との相互作用を取り入れるのに必要な原子、数千個規模のシミュレーションを実現することができなかった」という。

そこで富士通研究所では、より大規模な構造でも第一原理計算による電気特性予測を可能にする技術の開発を実施。今回、計算精度を保ちながら計算に利用するメモリ量を削減する計算手法と、スパコンの活用により、従来比3倍となる3000原子規模に対応する電気特性シミュレーション技術を開発した。

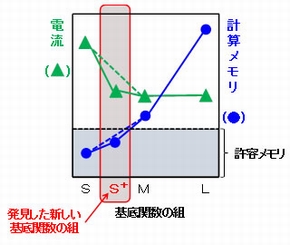

電気特性シミュレーションでは、電気の流れを表すために基底関数の組を用いる。通常、基底関数の数が増えると計算結果の得られる電流値は正しい値に近づいていくが、一方で使用する計算メモリ量が増加してしまう。今回、富士通研究所では計算精度を保持しながら、計算メモリを約1/4、計算時間を約1/25に削減できる基底関数の組を発見したとする。「基底関数の組の発見により、利用メモリを汎用スパコンの許容メモリ以下にすることができ、3000原子規模のナノデバイスの電気特性を約20時間で予測することが可能になった」という。富士通研究所では、今回の技術を用いて、グラフェンと絶縁膜で構成された3030原子からなるナノデバイスの電気特性のシミュレーションを実施するなどしている。

今後の技術開発などについて富士通研究所では、「計算機の性能向上に足並みを合わせたさらなる大規模並列化技術の開発により、より大規模で効率的な計算を追求し、数年中にナノデバイス全体のシミュレーションを達成すること(1万原子規模)で、計算機上でのナノデバイス設計の実現を目指す」としている。

関連記事

スパコン「京」で重レアアースレス磁石開発を加速!

スパコン「京」で重レアアースレス磁石開発を加速!

富士通は、スーパーコンピュータ「京」を用いて、永久磁石が磁化反転する課程を大規模にシミュレーションすることに成功したと発表した。これにより、磁性体を詳細に解析できるようになり、重レアアースを使用しない強力なネオジム磁石など新たな磁性材料の研究開発が促進されるという。 「高周波シミュレータがあれば設計できる?それは錯覚」、アイラボ市川氏が語る

「高周波シミュレータがあれば設計できる?それは錯覚」、アイラボ市川氏が語る

高周波回路の設計に使うシミュレータは近年、高機能・高性能化している。実際、高周波にそれほど詳しくないエンジニアでも、見よう見まねで回路を入力し、最適化処理を実行すれば、それなりの特性が得られる。「しかしそれは“回路設計”ではない。単なる“シミュレーション作業”だ」。アイラボラトリーの市川裕一氏はこう指摘する。 富士通研、書籍を裁断せずに歪みなく電子化する技術

富士通研、書籍を裁断せずに歪みなく電子化する技術

富士通研究所などは、厚みのある冊子を撮影するだけで、歪みのないフラットな書面として電子化できる画像補正技術を開発したと発表した。書籍を裁断することなく、書籍の各ページを歪みのない読みやすい書面データとして電子化できるようになる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

- パワー停滞も光デバイス堅調、三菱電機の半導体部門

次世代デバイスの一例とその原子規模例 出典:富士通研究所

次世代デバイスの一例とその原子規模例 出典:富士通研究所 今回、富士通研究所が発見した新しい基底関数の組の効果を示す図 出典:富士通研究所

今回、富士通研究所が発見した新しい基底関数の組の効果を示す図 出典:富士通研究所