ムーアの法則、28nmが“最後のノード”となる可能性も:ビジネスニュース オピニオン(1/2 ページ)

ムーアの法則というのは、そもそも「部品コストを最小限に抑えるための複雑さ」を示すものだ。その観点で考えると、実質的には28nmが“最後のノード”になる可能性がある。

ムーアの法則の終えんが近づいている――。近年、こうした予測をよく耳にする。その大半は、「2020年に7nmノードで終わりを迎える」というものだ。しかし、「実質的には、28nmノードがムーアの法則の最後のノードになる可能性がある」ということを認識しておく必要がある(関連記事:「ムーアの法則は間もなく終えんを迎える」、BroadcomのCTOが語る)。

もちろん、28nmプロセス以降も、より微細なトランジスタを作製し、より多くのトランジスタを1枚のウエハーから取ることは可能だ。しかし、コストは膨れ上がる一方になる。

“ムーアの法則”の本質

有名なムーアの法則は、Gordon Moore氏が1965年に発表した「The future of integrated electronics(集積電子工学の未来)」という論文の中で発表された。

同論文の中で、Moore氏は、「部品当たりのコストを最小限に抑えるには、複雑さが毎年約2倍ずつ増す。この比率は当面は増加せず、現在の比率が続くと予想される。長期的に見ると、この比率は不確定にはなるが、少なくとも今後10年間はほぼ一定の比率が維持されるだろう」と述べている。

ムーアの法則は、そもそも「部品コストを最小限に抑えるための複雑さ」についての記述なのである。そして、過去何年もの間、最小限の部品コストは28nmノードで止まっている。

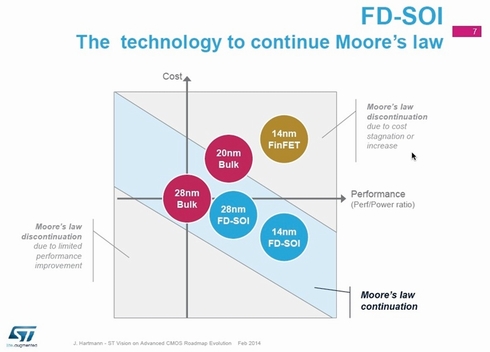

下のチャートは、半導体関連の業界団体であるSEMI(Semiconductor Equipment and Materials International)がオーストリアのザルツブルグで2014年2月23〜25日に開催した半導体関連のシンポジウム「ISS Europe 2014」で、STMicroelectronics(以下、ST)のJoel Hartmann氏が発表したものである。Hartmann氏は、STで製造およびプロセス技術の研究開発部門と組み込みプロセッシングソリューション部門のシニアバイスプレジデントを務める。

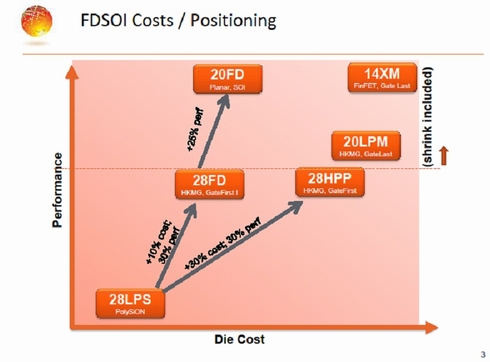

同氏は、「コストの停滞または上昇のためにムーアの法則が継続できなくなっている。これは、バルク技術にも当てはまる」と述べている。STのこの情報は、2013年に京都で実施された「SOI コンソーシアム」でGLOBALFOUNDRIESが発表した次のチャートでも裏付けられている。

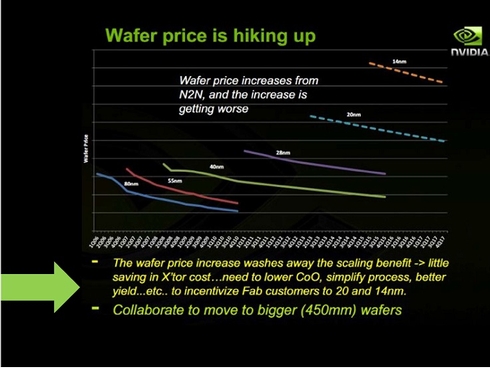

GLOBALFOUNDRIESのこのチャートからは、最も低コストのトランジスタが製造できるのはpolySiONプロセスの28nmノードが適用された場合であることが分かる。28nmより微細なスケーリングになると、二重露光リソグラフィや高誘電率膜/金属ゲート(HKMG:High-k/Metal Gate)、FinFETプロセスの適用に非常にコストがかかってしまう。また、2013年12月に日本で開催された「Semicon Japan」でNVIDIAが発表したチャートからは、微細化に伴ってウエハーの価格が大きく上昇することが分かる。

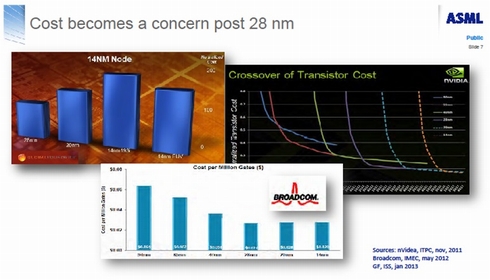

2013年に開催された「Semicon West」でASMLが発表したスライドは、微細化によってトランジスタの集積度を2倍にしても、ウエハー価格の上昇で利益が相殺されてしまうことを示している。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増