「ムーアの法則は間もなく終えんを迎える」、BroadcomのCTOが語る:ビジネスニュース オピニオン

BroadcomのCTO(最高技術責任者)が、「ムーアの法則はあと15年ほどで終えんを迎える。半導体プロセスの微細化は、5nm以降はほぼ進歩しない」という見解を示した。

BroadcomのCTO(最高技術責任者)であるHenry Samueli氏が、イーサネット技術の誕生40周年を記念するイベントにおいて、半導体業界の展望を語った。同氏は、半導体業界を「パーティーはまだ終わっていないが、そろそろタクシーを呼んだ方がいい時間に差し掛かったころ」と例えている。

Samueli氏は、イベント会場のステージ上のインタビューで、驚くほど率直に見解を語った。

同氏は、会場に集まったシリコンバレーの数十人の技術専門家たちに向けて、「ムーアの法則が終えんを迎える日は近い。われわれに残されている時間は、せいぜい15年程度だ。標準的なシリコンCMOSトランジスタの微細化は5nm前後までで、その後はほとんど進歩がみられなくなるだろう」と語った。

これまでにも数多くの専門家たちが、CMOS微細化の限界を予測してきた。しかし、大手半導体メーカーのベテラン幹部であり技術分野への造詣が深い人物が、こうした見解を示すのは、極めてまれなことだ。Samueli氏は、1991年に共同創設者としてBroadcomを設立する以前は、米国カリフォルニア大学ロサンゼルス校(UCLA)の電気工学部教授を務め、通信チップを専門分野としていた。

Samueli氏は、イベント会場でのパネルディスカッションを終えた後、EE Times誌のインタビューに応じ、「私にとって、CMOSトランジスタの微細化の終えんは、かねてから最大の関心事の1つだった。これについては、当社の顧客に対しても説明を重ねている」と述べた。

同氏は顧客に向けて、「20nm世代以降の最先端の半導体プロセスで製造するチップは、製造コストの増大により価格が上昇する」と説明してきたという。米国の市場調査会社であるGartnerが最近発表した試算によると、「工場の製造能力がウエハー換算で平均月産4万5000枚の場合、プロセスノードが1つ進むと製造コストが約5億米ドル増加する」という。配線のエッチングに、二重露光や三重露光といったマルチパターニングが必要になるからだ。

Samueli氏は、「チップを積層する3D(3次元)実装は一時的にチップの性能を上げることはできる。だが、コストは高くなる」と指摘する。Broadcomは、ハイエンドのスイッチチップに光インタフェースを3D実装したものを開発中だという。2015年以降に市場に投入する見込みだ。

Samueli氏の他に、同じくパネリストとして、スイッチメーカーであるBrocade Communications Systemsのチェアマンを務めるDave House氏も参加した。同氏は、Intelに23年間勤めた実績を持つエンジニアで、Samueli氏と同様に長く半導体業界に身を置いてきたベテランである。

House氏は、Broadcomの見解に対して、「今後10〜15年間の見通しを持つことは可能だ。しかし、それ以降に生じるであろうCMOS微細化の問題に対して、どう対処すべきかは分からない状態にある」と述べた。

House氏はIntel時代に、Intelの共同創設者でありムーアの法則の提唱者であるGordon Moore氏と定期的に交流していたという。

House氏は、「1970年代、『ムーアの法則があらゆる問題を解決してくれる』と考えていた私に、Moore氏は『10年後もこの法則が続くとは思わない』と言った。“10年後には微細化が終わる”というのは、Moore氏の口ぐせだった」と述べる。

「いつの時代も、十分な開発費と優秀なエンジニアがいた。“5nm”は確かに微細化の1つの壁かもしれないが、だからといって、微細化が5nmで本当に終わるのかどうかは分からない」(House氏)。

【翻訳:田中留美、編集:EE Times Japan】

関連キーワード

ムーアの法則 | Broadcom | 半導体 | Intel | CMOS | 3D | ビジネスニュース(EE Times Japan) | オピニオン(エレクトロニクス) | Gartner

関連記事

ムーアの法則はもう限界? リソグラフィ技術開発が追い付かず

ムーアの法則はもう限界? リソグラフィ技術開発が追い付かず

半導体の技術革新の源となってきたムーアの法則だが、さすがに限界が見え始めている。その原因の1つがリソグラフィ技術開発の遅れだ。 「ムーアの法則は今後10年以上は続く」、Intelが“限界説”を否定

「ムーアの法則は今後10年以上は続く」、Intelが“限界説”を否定

“ムーアの法則の終えん”がささやかれて久しいが、IntelのシニアフェローであるMark Bohr氏は、「CMOSのスケーリング(微細化)は少なくとも10年以上は続く」と分析している。 「ムーアの法則継続のために」、ASMLがSamsung/TSMCに自社株の売却交渉

「ムーアの法則継続のために」、ASMLがSamsung/TSMCに自社株の売却交渉

Intelに株式の15%を売却することが決定しているASMLは、Samsung、TSMCともASMLの株式売却と研究資金の投入について交渉を進めていると発表した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- 「世界2位」は実現するか、ローム、東芝、三菱電機とデンソーの選択は

- Musk氏は「半導体製造の再定義」を目指すのか

- 世界半導体市場は26年2月に大幅成長、日本のみ9カ月連続マイナスに

- ローム、8インチSiC MOSFET開発の技術目標を2年前倒しで達成

- 米Waymoの世界展開は東京から 「開始まで何年もかからない」

- 300mmファブ装置の投資額、2年連続で2桁成長へ

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- Intelがアイルランド工場を完全子会社化、Apolloから49%買い戻し

- シャープ新社長は海外事業出身 鴻海と連携で「新たな成長ステージへ」

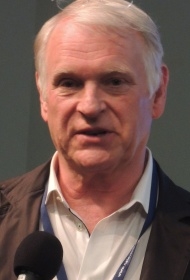

BroadcomのHenry Samueli氏(左)

BroadcomのHenry Samueli氏(左) Brocade Communications SystemsのDave House氏

Brocade Communications SystemsのDave House氏