Intelの14nm世代CPU「Core M」、厚さ9mmのタブレットが実現可能に:プロセス技術(1/2 ページ)

Intelが14nmプロセスを用いたCPU「Core M」(開発コード名「Broadwell-Y」)の概要を発表した。同社にとっては、22nmプロセスの「Haswell」に続き、第2世代となるFinFET(「トライゲートトランジスタ」)である。

2014年8月11日(米国時間)に、14nmプロセスを採用したCPU「Core M」(開発コード名「Broadwell-Y」)の概要を公開したIntel。米国オレゴン州にある同社の製造施設は、既に14nmプロセスに対応した生産能力を備えているとしている。

Intelによれば、14nmプロセスを用いることで、新しいx86ベースで9mm以下という薄さを持つ2in1タブレット端末/ノートPCを実現できるという。こうした製品は、2014年内に店頭に並ぶ見込みだ(関連記事:タブレットに注力するインテル、14nmプロセスの「Core M」も年内に出荷開始か)。

Broadwellの詳細については、Intelが2014年9月に米国カリフォルニア州サンフランシスコで開催する開発者向けカンファレンスで発表される予定だ。今回は、下記のように、14nm FinFETの仕様の一部が明らかになった。

- フィン間隔:42nm(22nmプロセスに比べ70%に微細化)

- ゲート間隔:70nm(22nmプロセスに比べ78%に微細化)

- インターコネクト間隔:52nm(22nmプロセスに比べ65%に微細化)

- フィンの高さ:42nm(22nmプロセスでのフィンの高さは34nm)

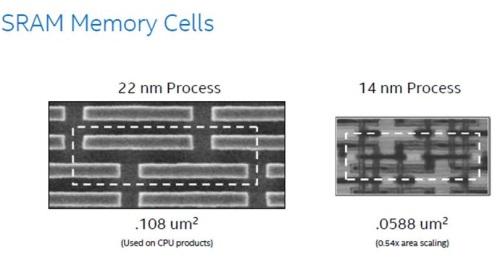

これらにより、14nmプロセスでSRAMセルを製造した場合、面積は0.0588μm2になる。22nmプロセスに比べて約54%に縮小される。

14nmプロセスを用いた製品の量産開始は、歩留まりの問題で1年近く遅れている。Intel ロジック開発部門のシニアフェローであるMark Bohr氏は、「これまでと同様に積極的にゲート間隔とフィン間隔を縮小したため、歩留まりの面で課題が生じていた。現時点は非常に良好な範囲にあり、今後も改善を図っていく」と述べている。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

14nmプロセスでSRAMセルを製造した場合、面積は0.0588μm2になる

14nmプロセスでSRAMセルを製造した場合、面積は0.0588μm2になる 14nmウエハーを掲げるMark Bohr氏

14nmウエハーを掲げるMark Bohr氏