CMOSイメージセンサーが引っ張る3次元積層技術:ビジネスニュース 業界動向(1/2 ページ)

チップを積層し、TSV(シリコン貫通電極)などで接続する3次元IC技術。CMOSイメージセンサーでも、3次元化が進んでいる。

これまで最先端プロセス技術の分野でリーダー的な位置付けを獲得してきたのは、プロセッサやメモリだ。しかし現在、CMOSイメージセンサーがそれに取って代わろうとしている。スマートフォンやタブレット端末、医療用機器、自動車など、あらゆる市場において、CMOSイメージセンサーの需要が高まっているためだ。

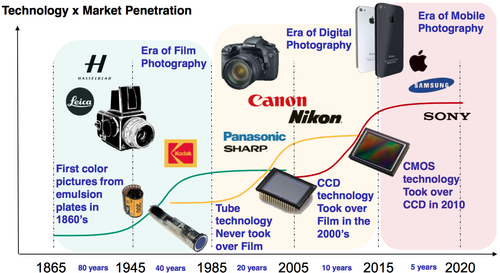

イメージング技術ではかつて、フィルムが使われていた。しかし、固体撮像素子が出現したことによって飛躍的な成長を遂げてきた。

注目集まる3次元IC

こうした中で成長しているのが、3次元(3D)積層技術だ。例えば、Micron Technologyの「Hybrid Memory Cube(HMC)」は、コントローラとDRAMチップをシリコン貫通電極(TSV:Through Silicon Via)で接続している。だが、CMOSイメージセンサーでは、ピクセルアレイ用に金属相互接続配線されたウエハーの、銅-銅接合(copper-to-copper bonding)を実現した点で、プロセッサやメモリにおける3次元積層技術の一歩先を行っているといえるだろう。

フランスの市場調査会社Yole DéveloppementのアナリストであるPierre Cambou氏は、EE Timesのインタビューに対し、「現在のところ、3次元積層では、上のウエハーと下のウエハーを接続するのに、TSV技術を採用している。2つのビアは、それぞれの接続に不可欠であり、2層間を橋渡しする役割を担う。2つのビア間の金属結合は、チップの表面で行っている」と述べている。

銅-銅接合でレイヤー間を接続できるようなウエハー積層技術が完成すれば、CMOSイメージング業界は、プロセッサ/メモリ業界ではまだ普及すらしていないTSV技術が“時代遅れ”になってしまう可能性もあるのだ。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

イメージング技術の推移 出典:Yole Développement

イメージング技術の推移 出典:Yole Développement