EE Times Japan >

マイコン >

ルネサス、28nm世代混載フラッシュ技術を改良――順調に進む次世代車載マイコン開発:プロセッサ/マイコン(2/3 ページ)

» 2015年02月25日 13時30分 公開

[竹本達哉,EE Times Japan]

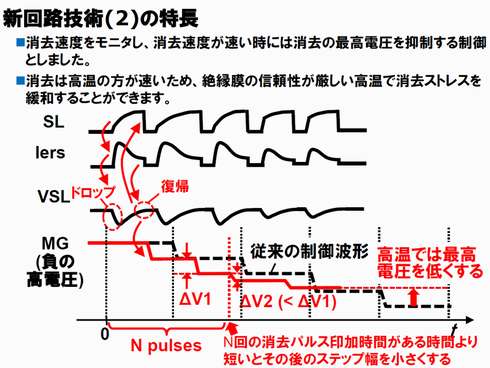

消去ストレスの緩和技術を開発

消去速度を監視し、消去が速い時は消去の最高電圧を抑制するよう制御することで、絶縁膜が受ける厳しい高温での消去ストレスを緩和する技術を新たに開発した。この技術により、微細化に伴うメモリセルや高電圧メタル配線間の絶縁膜の薄膜化による消去時の高電圧ストレスによる耐性低下を抑えた。

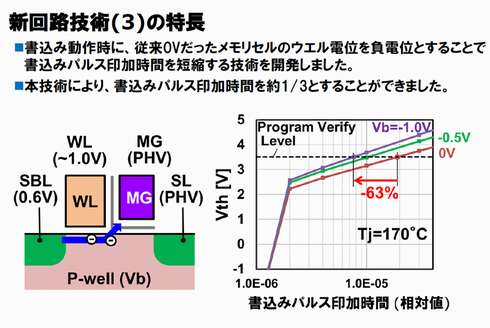

書き込みの高速化技術を開発

書き込み動作時にメモリセルのウエル電位を負電圧とすることによる書き込みパルス印加時間短縮と、複数のフラッシュモジュールの並列書き込みによる高速書き込み技術を開発した。これにより、混載フラッシュとしては最速の書き込みスループットとなる2.0Mバイト/秒を達成した。

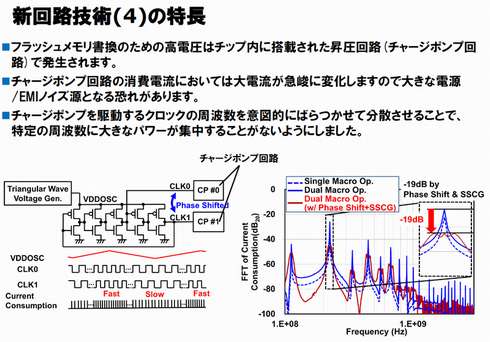

書き換え時の電源/EMIノイズ低減技術を開発

無線を介した遠隔操作「OTA(over-the-air)」によるプログラム更新など、製品出荷後のプログラムの書き換えが増加することが予想される中で、「電源/EMIノイズによるシステム全体(フラッシュマイコン搭載機器)の動作への影響を最小限に抑える必要がある」(ルネサス)とする。そこで、フラッシュ書き換えのための高電圧を発生する昇圧回路の駆動クロックをSSCG(spread-spectrum clock generation)化し、フラッシュ書き換え時の電源/EMIノイズを大幅に低減する技術を開発した。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

Special SitePR

あなたにおすすめの記事PR