次世代3次元SoCは、TSVを使わない――Qualcomm:プロセス技術(1/2 ページ)

Qualcommは、米国で開催された「International Symposium on Physical Design(ISPD)」で、同社の3次元SoCの技術動向について語った。TSV(シリコン貫通ビア)を使わずに積層することで、小型化と歩留まりの向上を実現したいという。

Qualcommのエンジニアリング部門でバイスプレジデントを務めるKarim Arabi氏は、2015年3月29日〜4月1日に米国カリフォルニア州モントレーで開催された「International Symposium on Physical Design(ISPD)」で、同社の3D VLSI(Very Large Scale Integration)を用いたSoCの技術動向について語った。

Arabi氏は、EE Timesに対して、「当社の3D VLSI技術(Qualcommは「3DV」と呼ぶ)は、ダイサイズを半分に縮小し、歩留まり率を上げることができる」と話している。

同氏によると、Qualcommは、2018年には80億台に達すると予想されるスマートフォン市場に狙いを定めているという。2018年にはスマートフォンの製造台数は、コンピュータとその他の電子機器の合計台数を上回るとされている。「音声認識アプリのようなコンピューティング処理に優れたアプリケーションをクラウドで利用できるとしても、スマートフォン本体のプロセッシング能力の必要性はさらに高まる」と同氏は指摘する。

Qualcommは長期にわたり、人間の脳をモデルにしたNPU(ニューラル処理装置)の開発に取り組んでいる。Arabi氏はその理由について、「人間の脳は、次世代モバイル機器やクラウドコンピューティング、ビッグデータの処理、ディープラーニング(深層学習)、マシンラーニング(機械学習)に求められる高度な柔軟性と効率性を備えているからだ」と説明している。ただし同社は、「当面は従来品のSoCの性能向上と、3DVのインターコネクト技術、プロセス技術の開発に取り組む」としている。

同社は現在、2016年の市場投入を目指して、2種類の3DVインターコネクト技術を開発している。2種類の3Dインターコネクト技術とは、face-to-back(F2B)とface-to-face(F2F)である。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

QualcommのKarim Arabi氏は、「次世代のSoCは、TSV技術を使わずに、3層までを積層するものになるだろう。TSVを使わないことで、小型化と歩留まりの向上が可能になる」と話す

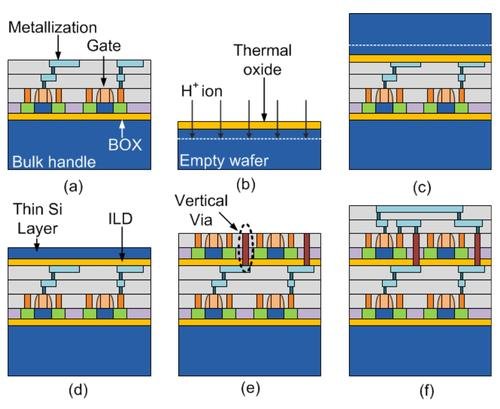

QualcommのKarim Arabi氏は、「次世代のSoCは、TSV技術を使わずに、3層までを積層するものになるだろう。TSVを使わないことで、小型化と歩留まりの向上が可能になる」と話す F2Bの製造工程。(a)下位層は2D ICと同じように作られる。(b)〜(d)層を追加するには、シリコンの薄膜を下位層の上に積層する。(e)上層のFEOL(Front End of Line:基板工程)では、通常の垂直ビアで接続できる。(f)BEOL(Back End of Line:配線工程)で上位層を形成する 出典:Qualcomm

F2Bの製造工程。(a)下位層は2D ICと同じように作られる。(b)〜(d)層を追加するには、シリコンの薄膜を下位層の上に積層する。(e)上層のFEOL(Front End of Line:基板工程)では、通常の垂直ビアで接続できる。(f)BEOL(Back End of Line:配線工程)で上位層を形成する 出典:Qualcomm