ARMから見た7nm CMOS時代のCPU設計(10)〜PVTコーナーの増加がタイミング解析を難しくする:福田昭のデバイス通信(21)(1/2 ページ)

回路の動作周波数などを左右する大きな要因は「PVT」、つまりプロセス(P)、電源電圧(V)、温度(接合温度T)である。動作周波数の代表値や最高値、最低値は、PVTコーナーの数によって決まる。この数は、微細化とともに急増する傾向にあり、タイミング解析がより難しくなっている。

動作周波数(または遅延時間)を決める条件

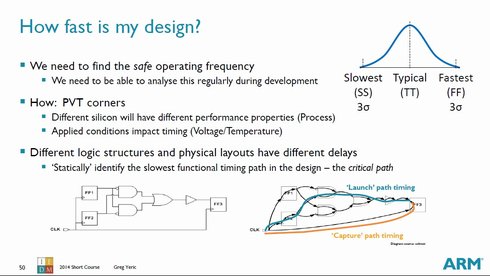

設計作業でエンジニアは、LSIが確実に動作する周波数、あるいは遅延時間の範囲を見つけなければならない。設計技術者は、動作周波数やタイミングなどを解析する設計ツール(EDAツール)を使用し、回路が動作する周波数あるいは遅延時間の範囲を検証する。

回路の動作周波数や遅延時間などを左右する大きな要因は、プロセス(P)と電源電圧(V)、温度(接合温度T)である。これらをまとめて「PVT(Process-Voltage-Temperature)」と略記することが少なくない。まずプロセスの違いによって回路性能は異なる性質を帯びる。そして電源電圧が上下すると、回路の性能が変動する。温度が変化しても、回路の性能は変化する。

PVTのほかにも、動作周波数や遅延時間などを変動させる要因は存在する。例えば論理アーキテクチャと物理的なレイアウトである。1つの信号が分岐し、異なる経路(パス)を通過して合流するときは、一般的には段数の多い経路を通過する信号が合流地点までに要する時間が長い。ここでは段数の多い経路が遅延時間を決めるクリティカルなパスとなる。

PVTコーナーが動作周波数の範囲を決める

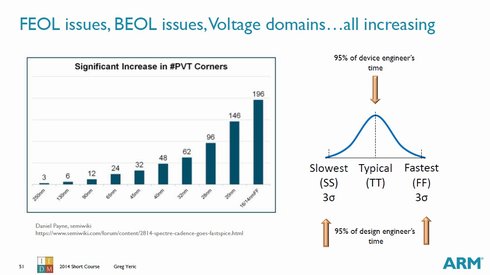

PVTの違いによって動作周波数(あるいは動作速度)には、ばらつきが生じる。ばらつきが確率的な分布で決まる場合には、代表値(TT)を中心とするσ(標準偏差)のプラスマイナス3倍までの範囲が、製品の仕様となる。プラス3σの値が動作速度の最高値(FFあるいはFastest)。そしてマイナス3σの値が動作速度の最低値(SSあるいはSlowest)となる。LSIの設計技術者はほぼすべて、このプラスマイナス3σで決まる範囲を意識している。これに対し、デバイス技術者は代表値(TT)だけに注目していることが少なくない。

基本的には、SS(最低速度)は遅いプロセスと低い電源電圧、高い温度というPVT条件で決まる。反対にFF(最高速度)は例えば、速いプロセスと高い電源電圧、低い温度というPVT条件で決まる。PVT条件が少ないときはタイミングの解析は容易だが、PVT条件が多くなるとタイミング解析が複雑になり、従来からの解析手法である静的タイミング解析では、設計が困難になる。

SSとTT、FFを決めるPVTコーナーの数は、微細化とともに急激に増加する傾向にある。すなわちタイミング解析が難しくなる。130nm世代ではPVTコーナーの数は6個に過ぎなかった。それが最先端の量産世代である28nm世代では、96個ものPVTコーナーが存在する。PVTコーナーの数は20nm世代では146個、16/14nm世代では196個といった膨大な数になると予測されている。このため、PVTのばらつきを考慮した統計的なタイミング解析手法が、最近のLSI設計では利用されるようになった。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- 「世界2位」は実現するか、ローム、東芝、三菱電機とデンソーの選択は

- Musk氏は「半導体製造の再定義」を目指すのか

- 世界半導体市場は26年2月に大幅成長、日本のみ9カ月連続マイナスに

- ローム、8インチSiC MOSFET開発の技術目標を2年前倒しで達成

- 米Waymoの世界展開は東京から 「開始まで何年もかからない」

- 300mmファブ装置の投資額、2年連続で2桁成長へ

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- Intelがアイルランド工場を完全子会社化、Apolloから49%買い戻し

- シャープ新社長は海外事業出身 鴻海と連携で「新たな成長ステージへ」