ARMから見た7nm CMOS時代のCPU設計(13)〜高移動度FinFETの期待と現実:福田昭のデバイス通信(24)(1/2 ページ)

FinFETの“延命策”として、チャンネルの材料をシリコンからゲルマニウム(Ge)やインジウム・ガリウム・ヒ素(InGaAs)などに変更する方法がある。だが、ARMの講演では、この“延命策”に悲観的だった。今回は、Ge FETなどが抱える問題と、その打開策について紹介する。

移動度の高さをコンタクト抵抗の増加が打ち消す

前回は、14nm世代から5nm世代にかけてトランジスタの仕様がどのように推移していくかを示した。それから、FinFET(フィンフェット)の延命策を説明した。

FinFETの延命策は、チャンネルの材料をシリコン(Si)から、キャリア移動度の高い別の材料に変更することだと、前回は述べた。ゲルマニウム(Ge)やインジウム・ガリウム・ヒ素(InGaAs)などがその候補である。

しかしARMの講演では、こういった移動度の高い材料を使ったトランジスタの将来性には悲観的だった。それはLSI、つまり大規模集積回路の性能(動作周波数あるいは遅延時間)を支配する要因が、トランジスタ本体の性能ではなくなるからだ。LSIの性能を支配するのは、寄生素子の抵抗(R)と容量(C)になる。7nm時代のCPUをはじめとする大規模ロジックの性能は、RC積によって左右されるようになる。もちろん、RC積を小さくすることが望ましい。しかし現実には、LSIのRC積は増加していく。

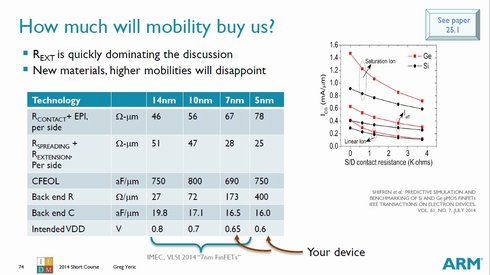

14nm世代から10nm世代、7nm世代と微細化することによって増加する寄生素子は大きく分けると、以下の2つだとしていた。コンタクト抵抗と配線抵抗である。ARMの講演スライドによると、コンタクトまわりの抵抗率は14nm世代と7nm世代では、7nm世代が1.5倍近くに増加する。フロントエンドオブライン(FEOL)の容量(単位長当たり)は、14nm世代と7nm世代ではほとんど変わらない。

トランジスタのドレイン電流(単位長当たり)をGeトランジスタとSiトランジスタで比較すると、コンタクト抵抗0.5kΩ以下と低い領域では飽和電流と実効電流は1.5倍強の差が生じる。ところがコンタクト抵抗が増加するにしたがって両者の差は縮む。コンタクト抵抗が3kΩを超えると、両者の差はわずかなものになってしまう。チャンネル材料をSiからGeに変更しても、コンタクト抵抗を下げないと変更した意味がなくなることが分かる。

深刻なのはバックエンドオブライン(BEOL)、粗く言ってしまえば多層金属配線の抵抗である。14nm世代と7nm世代では、抵抗(単位長当たり)は6.4倍にも増える。容量(単位長当たり)はわずかに減少するものの、遅延時間を左右するRC積は大幅に増加することになる。例えば7nm世代のRC積は、14nm世代の5.3倍に達する。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 「装置は動くがプロセスが成立しない」――He供給危機とナフサ不足の本質

- He/ナフサ供給危機で工場新設も遅延? 装置/チップメーカーへの波及経路を探る

- 最新ノートPC5機種を分解 新旧MacBook Proの中身の違いは?

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 「AI特需」の恩恵届かぬ日本企業 Gartnerが見る2026年半導体市場

- 「Rapidusの隣」に光電融合パッケージ開発拠点、28年度の完成目指す

- Apple新CEOはエンジニア出身 製品開発重視への回帰か

- ローム・東芝・三菱電機のパワー半導体はどうなるか

- シリコンフォトニクスと先進パッケージの統合が描く未来