ARMから見た7nm CMOS時代のCPU設計(13)〜高移動度FinFETの期待と現実:福田昭のデバイス通信(24)(2/2 ページ)

ゲルマニウム・トランジスタではリーク電流が増大

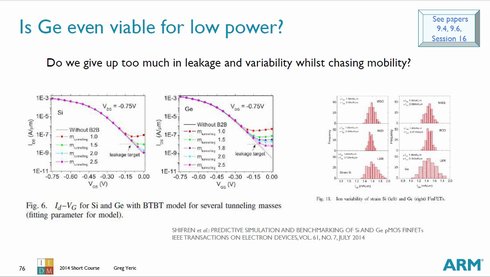

ゲルマニウム(Ge)FETが抱える問題は、他にもある。リーク電流がシリコン(Si)FETに比べると高いことだ。リーク電流の要因の一つであるバンド間トンネリングでは、ゲート電圧が低い領域ではSiよりもGeのリークが大きい。待機時消費電力の制約が厳しいモバイル用CPUでは、Ge FETのリーク電流は無視できない。

トランジスタ間の特性ばらつき(オン電流のばらつき)は、Si FETと比べてGe FETが特に小さいわけではない。むしろ、ばらつきはSi FETよりもGe FETがやや大きい。この点も問題である。

左はトランジスタにおけるドレイン電流とゲート電圧の関係。左がSi FET、右がGe FET。バンド間トンネリングによるリーク電流を比較した。右はオン電流のばらつき。左がSi FET、右がGe FET(クリックで拡大) 出典:ARM

左はトランジスタにおけるドレイン電流とゲート電圧の関係。左がSi FET、右がGe FET。バンド間トンネリングによるリーク電流を比較した。右はオン電流のばらつき。左がSi FET、右がGe FET(クリックで拡大) 出典:ARM低ゲート電圧での解決策としてトンネルFETが浮上

そこで代替策として、従来とは異なる原理でトランジスタ電流をオン・オフするFETの研究が進められている。従来のMOSFETでは、ゲート電圧によるポテンシャルの変化を利用してソースからチャンネルに対して少数キャリア(nチャンネルMOSでは電子)を注入していた。

ポテンシャルの変化を利用したキャリア注入は、ゲート電圧が高いときは非常に上手く働く。しかしゲート電圧が低くなるとポテンシャルの変化がわずかになり、キャリアの注入が減る。すなわち、トランジスタ電流が低下する。

この問題の解決策として浮上したのが、ポテンシャルではなく、トンネル効果を利用してキャリアを注入するトランジスタである。トンネルFET(TFET)と呼ばれている。トンネルFETでは、低いゲート電圧でもドレイン電流が急峻に立ち上がる。

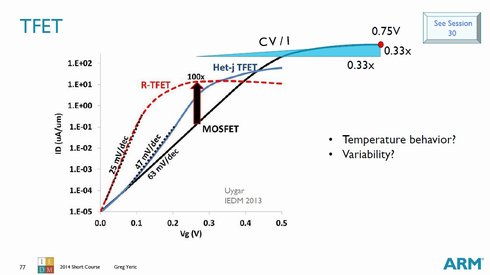

ゲート電圧が0Vから増加するときに、電流の立ち上がりの急峻さは「SS(Subthreshold Swing)」あるいは「S係数」と呼ぶ数値で示すことが多い。具体的には、電流が一桁増えるのに必要なゲート電圧の増加量(mV/dec)である。この値が低いほど、電流が急峻に立ち上がる。

ARMの講演では、従来のMOSFETのSSが63mV/decであるのに対し、トンネルFETのSSは25mV/decと低い。例えば0.25V〜0.3Vのゲート電圧で比較すると、トンネルFETのドレイン電流(単位長当たり)は、従来のMOSFETの約100倍にも達する。

(次回に続く)

関連記事

FinFET以降の半導体製造技術はどう進む? IBMの見解

FinFET以降の半導体製造技術はどう進む? IBMの見解

「Common Platform Technology Forum」において、IBMが半導体製造技術の将来展望について発表を行った。液浸リソグラフィによるダブルパターニング技術やFD-SOI技術に加え、カーボンナノチューブ、シリコンフォトニクス、ナノワイヤーなどのキーワードを交えて半導体製造の将来像や課題などが示された。 ムーアの法則、半数以上が「22nm以降では難しい」――半導体業界リーダー調査

ムーアの法則、半数以上が「22nm以降では難しい」――半導体業界リーダー調査

オランダのKPMGが半導体業界のビジネスリーダーを対象に調査したところ、「ムーアの法則の有用性は存続する」と予想しているのは、回答者の1/4で、半数以上が「22nmプロセス以降では、ムーアの法則の存続は難しい」と考えていることが分かった。 ムーアの法則、その行方を聞く

ムーアの法則、その行方を聞く

これまで何度となく“終えん説”が唱えられてきたムーアの法則だが、半導体業界は多大な労力でこの法則を維持している。今後、ムーアの法則はどうなっていくのか。業界のキーマンに、ムーアの法則の行方や、ムーアの法則の維持に関わる技術などについて話を聞いた。 ムーアの法則は5nmに壁、民生用LSIは28nmで様子見を

ムーアの法則は5nmに壁、民生用LSIは28nmで様子見を

ムーアの法則についての見解を数多く述べているBroadcomのCTO、Henry Samueli氏。微細化技術の今後や、IoT市場の動向、同社のベースバンド事業撤退などについて、話を聞いた。 ムーアの法則はまだ終わらない、存続の鍵はGaAs材料

ムーアの法則はまだ終わらない、存続の鍵はGaAs材料

POET Technologiesは、ムーアの法則を続ける鍵になる材料として、GaAs(ガリウムヒ素)を挙げている。高いスイッチング周波数を実現できるだけでなく、光回路と論理回路を同一チップに集積できるという利点もある。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- DRAM不足で変わるAIシステム設計 エッジAIや特化型モデルに追い風

- ソニーセミコンとTSMCが合弁会社設立を検討

- 半導体検査装置向けレンズの研磨工程が稼働、生産能力2.6倍に

- 26年3月の世界半導体市場は79%増、日本も10カ月ぶりプラス成長