EE Times Japan >

僾儘僙僗媄弍 >

ARM偐傜尒偨7nm CMOS帪戙偺CPU愝寁乮15乯乣僆儞僠僢僾SRAM偺僗働乕儕儞僌栤戣丗暉揷徍偺僨僶僀僗捠怣乮26乯乮1/2 儁乕僕乯

崱夞偼丄SRAM偺旝嵶壔偵偮偄偰怗傟傞丅16/14nm悽戙傑偱偼旝嵶壔偑弴挷偵恑傫偱偒偨偑丄悢懡偔偺壽戣偑懚嵼偡傞丅廃曈夞楬傪弅彫偟偵偔偄偙偲偑丄偦偺1偮偲偟偰嫇偘傜傟傞丅

» 2015擭05寧29擔 13帪00暘 岞奐

[暉揷徍丆EE Times Japan]

CPU偵晄壜寚側僉儍僢僔儏儊儌儕偺撪憼

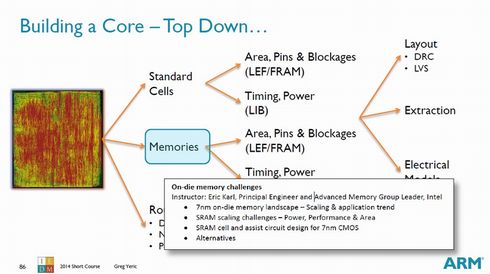

丂CPU愝寁偱偼儘僕僢僋愝寁偺傎偐偵丄儊儌儕愝寁偑懚嵼偡傞丅嬶懱揑偵偼丄僉儍僢僔儏儊儌儕傗僞僌儊儌儕側偳偺僆儞僠僢僾儊儌儕乮撪憼儊儌儕乯偺愝寁偱偁傞丅CPU偺僆儞僠僢僾儊儌儕媄弍偵偼夁嫀偐傜尰嵼傑偱偢偭偲丄庡偵SRAM媄弍偑巊傢傟偰偒偨丅SRAM媄弍偼儘僕僢僋偲僾儘僙僗偺屳姺惈偑偁傝丄側偍偐偮丄偒傢傔偰崅懍偵僨乕僞傪撉傒彂偒壜擻偱偁傞偐傜偩丅

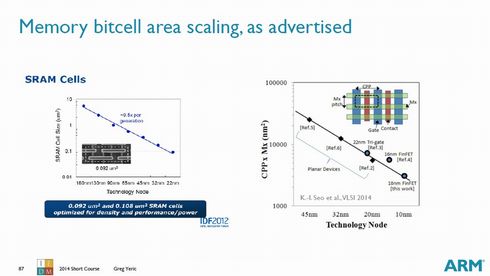

丂SRAM偺旝嵶壔乮僗働乕儕儞僌乯偼丄嵟怴悽戙偱偁傞16/14nm悽戙傑偱偼丄傎傏弴挷偵恑傫偱偒偨丅Intel偑岞昞偟偨僨乕僞偵傛傞偲丄SRAM僙儖偺僔儕僐儞柺愊偼丄旝嵶壛岺偺悽戙偑恑傓偛偲偵栺2暘偺1偵彫偝偔側偭偰偒偨丅偙偺僩儗儞僪偼180nm悽戙偐傜130nm悽戙丄90nm悽戙丄65nm悽戙丄45nm悽戙丄32nm悽戙丄22nm悽戙偲彮側偔偲傕6悽戙傕偺娫丄堐帩偝傟偰偒偨丅傑偨暿偺尋媶僨乕僞偵傛傞偲丄僎乕僩僺僢僠亊儊僞儖僺僢僠乮戞1憌嬥懏攝慄偺僺僢僠乯偱昞婰偝傟傞嬫夋偺柺愊偼丄45nm悽戙偐傜丄32nm悽戙丄22nm悽戙丄16nm悽戙丄10nm悽戙傑偱丄傎傏堦掕偺儁乕僗偱弅彫偱偒偰偄傞丅

丂SRAM僙儖偺僩儔儞僕僗僞偼32nm悽戙傑偱偼儘僕僢僋偲摨條偺僾儗乕僫宆FET偩偭偨丅22nm悽戙埲崀偼儘僕僢僋偲摨條偵丄FinFET偺摫擖偑巒傑偭偰偄傞丅偨偩偟FinFET偑杮奿揑偵摫擖偝傟傞偺偼丄16/14nm悽戙偐傜偵側傞偩傠偆丅

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

摿暿嫤巀PR

僗億儞僒乕偐傜偺偍抦傜偣PR

Special ContentsPR

Pickup ContentsPR

婰帠儔儞僉儞僌

- 僨儞僜乕丄儘乕儉偵懳偡傞姅幃庢摼採埬傪惓幃昞柧

- NVIDIA偲儊儌儕3幮丄悽奅敿摫懱攧忋崅偺42亾愯傔傞

- 傕偼傗敿摫懱儊乕僇乕偺堟傪挻偊偨丂NVIDIA嵟怴僄僢僕婡婍傪暘夝

- Arm偑敿摫懱偺帺幮奐敪偵嶲擖丄AI僨乕僞僙儞僞乕岦偗CPU敪昞

- 僉僆僋僔傾偑Nanya偵774壄墌弌帒丄DRAM挿婜嫙媼宊栺傪掲寢

- 嫑捗偼Tower丄搗攇偼Nuvoton偵丂TPSCo帠嬈偺嵞曇傪敪昞

- 僷儚乕敿摫懱嵞曇偑杮奿壔丂儘乕儉丒搶幣丒嶰旽揹婡偑嫤媍奐巒傊

- 乽Renesas 365乿偑偮偄偵巒摦 乽晄壜擻偩偭偨婯柾乿偺専徹丄悢暘偱

- 僜僯乕丒儂儞僟儌價儕僥傿丄EV乽AFEELA乿奐敪拞巭

- 僀儔儞愴憟偺挿婜壔偑敿摫懱嬈奅偵媦傏偡怺崗側塭嬁

Special SitePR

偁側偨偵偍偡偡傔偺婰帠PR