ARM偐傜尒偨7nm CMOS帪戙偺CPU愝寁乮15乯乣僆儞僠僢僾SRAM偺僗働乕儕儞僌栤戣丗暉揷徍偺僨僶僀僗捠怣乮26乯乮2/2 儁乕僕乯

廃曈夞楬偑弅彫偟偯傜偄

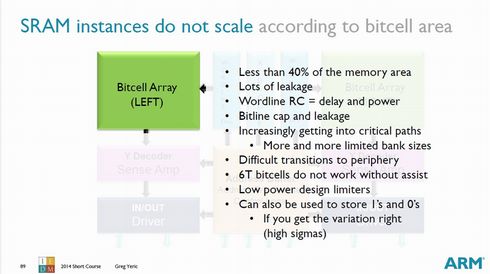

丂SRAM傪峔惉偡傞庡梫側晹暘偼儊儌儕僙儖傪儅僩儕僋僗忬偵攝抲偟偨儊儌儕僙儖傾儗僀偱偁傞丅侾屄乣4屄掱搙偺僽儘僢僋偵暘妱偝傟偨儊儌儕僙儖傾儗僀偼丄儊儌儕僙儖偑彫偝偔側傞偙偲偱偦偺傑傑僙儖傾儗僀慡懱偑弅彫偝傟傞丅尵偄姺偊傞偲丄斾妑揑扨弮偵弅彫偱偒傞丅偨偩偟SRAM偺峔惉梫慺偼儊儌儕僙儖傾儗僀偩偗偱偼側偄丅廃曈夞楬偑偁傞丅

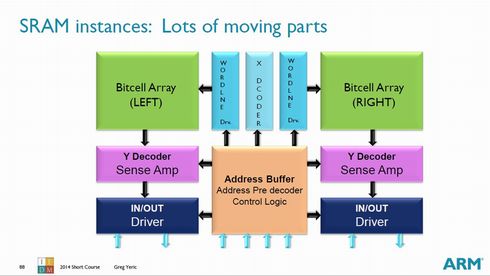

丂廃曈夞楬偵偼擖弌椡僶僢僼傽丄峴僨僐乕僟乮X僨僐乕僟乯丄儚乕僪慄僪儔僀僶丄楍僨僐乕僟乮Y僨僐乕僟乯丄僙儞僗傾儞僾側偳偑偁傞丅偙傟傜偺廃曈夞楬偺弅彫偼丄儊儌儕僙儖傾儗僀傎偳偵偼扨弮偵偼恑傑側偄丅椺偊偽儊儌儕僙儖傾儗僀偺僎乕僩攝慄傪嬱摦偡傞儚乕僪慄僪儔僀僶偼丄僩儔儞僕僗僞傪扨弮偵弅彫偡傞偲揹棳嬱摦擻椡偑掅壓偡傞丅僆儞僠僢僾僉儍僢僔儏偺婰壇梕検偑慜偺悽戙偺僔儕僐儞僟僀偲摍偟偗傟偽栤戣偼彮側偄傕偺偺丄幚嵺偵偼悽戙岎戙偵敽偭偰僆儞僠僢僾僉儍僢僔儏偺婰壇梕検傪奼戝偡傞偙偲偑懡偄丅偡傞偲儚乕僪慄偺攝慄掞峈偲攝慄梕検偑憹壛偟丄扨弮側弅彫偱偼儚乕僪慄偺揹棳嬱摦擻椡偑晄懌偡傞丅懳嶔偲偟偰偼儚乕僪慄僪儔僀僶偺僩儔儞僕僗僞傪戝偒偔偡傞丄儚乕僪慄傪暘妱偟偰僾儕僪儔僀僶傪憓擖偡傞丄側偳偑偁傞丅偨偩偟偄偢傟傕丄僔儕僐儞柺愊偺奼戝傪彽偔丅

丂偦偺傎偐偵傕壽戣偼悢懡偔懚嵼偡傞丅儚乕僪慄掞峈偲儚乕僪慄梕検偺栤戣偼愭偵弎傋偨捠傝偩丅價僢僩慄偺梕検偲儕乕僋揹棳偺憹壛傕栤戣偵側傞丅徚旓揹棳偺惂栺忦審傪枮偨偡偙偲偑擄偟偔側傞丅傑偨揹尮揹埑偺掅壓偵傛傝丄6屄偺僩儔儞僕僗僞偱峔惉偟偨儊儌儕僙儖偱偼丄傾僔僗僩側偟偱偼摦嶌偟側偔側傞偲偄偆寽擮傕偁傞丅儊儌儕僙儖傾儗僀偱偼僶儞僋偺戝偒偝偵懳偡傞惂尷偑尩偟偔側傞丅僋儕僥傿僇儖僷僗偺憹壛傪梷惂偡傞偨傔偱偁傞丅偽傜偮偒偺憹戝傕怱攝偩丅

乮師夞偵懕偔乯

娭楢婰帠

晄婗敪惈僷儚乕僎乕僥傿儞僌丄儊僯乕僐傾僾儘僙僢僒偺懸婡揹椡嶍尭偵埿椡

晄婗敪惈僷儚乕僎乕僥傿儞僌丄儊僯乕僐傾僾儘僙僢僒偺懸婡揹椡嶍尭偵埿椡

搶嫗岺嬈戝妛乮搶岺戝乯憸忣曬岺妛尋媶強偺悰尨憦弝嫵庼傜偺尋媶僌儖乕僾偲恄撧愳壢妛媄弍傾僇僨儈乕乮KAST乯偼丄晄婗敪惈僷儚乕僎乕僥傿儞僌乮NVPG乯偑儊僯乕僐傾偺僾儘僙僢僒傗SoC偺懸婡帪揹椡嶍尭偵嬌傔偰桳岠側傾乕僉僥僋僠儍偱偁傞偙偲傪幚徹偟偨丅 僯僢僠梡搑偺堟傪弌側偄MRAM丄晛媦偺尞偼僐僗僩偲婰榐枾搙

僯僢僠梡搑偺堟傪弌側偄MRAM丄晛媦偺尞偼僐僗僩偲婰榐枾搙

暆峀偄梡搑偱DRAM傗SRAM偺抲偒姺偊偵側傞偲梊憐偝傟偰偄傞MRAM乮帴婥掞峈儊儌儕乯丅嶻嬈梡搑傪拞怱偵嵦梡偑恑傫偱偄傞偑丄晛媦偑壛懍偡傞偵偼傑偩帪娫偑昁梫側傛偆偩丅 儊儌儕曇丗師悽戙戝梕検僼儔僢僔儏偲師悽戙崅懍DRAM偵拲栚

儊儌儕曇丗師悽戙戝梕検僼儔僢僔儏偲師悽戙崅懍DRAM偵拲栚

崱夞偼丄戝梕検壔偲崅懍壔偑恑傓敿摫懱儊儌儕偵徟揰傪摉偰傞丅儊儌儕巗応偺擇戝惃椡偲側偭偰偄傞DRAM偲NAND僼儔僢僔儏儊儌儕偵偮偄偰偺島墘偑懡偄丅15nm僾儘僙僗傪嵦梡偟偨NAND僼儔僢僔儏儊儌儕傗丄幵嵹儅僀僐儞岦偗僼儔僢僔儏儊儌儕媄弍丄師悽戙偺DRAM僀儞僞僼僃乕僗側偳偵娭偡傞敪昞偑偁傞丅 乽宱尡偱愝寁偡傞偲幐攕偡傞乿丄儖僱僒僗偑採帵偡傞16nm FinFET SRAM偺壽戣

乽宱尡偱愝寁偡傞偲幐攕偡傞乿丄儖僱僒僗偑採帵偡傞16nm FinFET SRAM偺壽戣

儖僱僒僗 僄儗僋僩儘僯僋僗偼丄16nm FinFET僾儘僙僗傪梡偄偰SRAM傪帋嶌偟偨偲敪昞偟偨丅僾儗乕僫宆MOSFET傪巊偆応崌偵斾傋偰掅偄摦嶌揹埑偱崅懍撉傒弌偟偵惉岟偟偰偄傞偑丄堦曽偱FinFET偲丄旝嵶壔僾儘僙僗傪梡偄偨偙偲偵傛傞壽戣傕憹偊偰偄傞丅

Copyright © ITmedia, Inc. All Rights Reserved.

婰帠儔儞僉儞僌

- 僀儔儞愴憟偺挿婜壔偑敿摫懱嬈奅偵媦傏偡怺崗側塭嬁

- 乽Renesas 365乿偑偮偄偵巒摦 乽晄壜擻偩偭偨婯柾乿偺専徹丄悢暘偱

- 崅NA EUV傪乽嶻嬈婯柾傊奼挘乿丄imec偑EXE:5200摫擖

- 搶幣偲偺嫤媍傗僨儞僜乕採埬傊偺懳墳丄儘乕儉偑怴惡柧

- 慡屌懱擇師揹抮偺乽200亷摦嶌乿傪幚墘丄擔杮揹婥徤巕

- AI/HPC僔僗僥儉偺巰柦傪惂偡傞徚旓揹椡丒曻擬愝寁乮慜曇乯

- AI偺嫞憟幉偼敿摫懱偐傜揹椡傊乗乗擔杮偺愴棯偺乽巰妏乿偵

- 僉僆僋僔傾偑挻崅IOPS SSD奐敪 NVIDIA Storage-Next偵懳墳

- NVIDIA偲儊儌儕3幮丄悽奅敿摫懱攧忋崅偺42亾愯傔傞

- ST偑乽拞崙惢STM32乿検嶻奐巒丄嫙媼栐傪尰抧姰寢