ARMから見た7nm CMOS時代のCPU設計(19)〜微細化なしで小型化を達成する3次元技術:福田昭のデバイス通信(30)(1/2 ページ)

微細化が限界を迎えた時に回路密度を向上する手法として、シリコンダイや回路層を積層する3次元技術がある。今回は、これらの手法を紹介していこう。

シリコンを変えずにシステムを小型化する

電子回路や電子機器などのボードとはふつう、ロジックやメモリ、アナログ、高周波(RF)といった複数の半導体チップをはんだ付けによってプリント配線基板に接続したモジュールを意味する。プリント配線基板の基板材料は樹脂であり、プリント配線は銅配線である。

これらの半導体チップは、ワンチップ(1枚のシリコンダイ)に集積しづらい。製造プロセスが異なるからだ。単純に1枚のシリコンダイにこれらの回路を集積すると、プロセスの工数が著しく増加し、製造コストが跳ね上がってしまう。

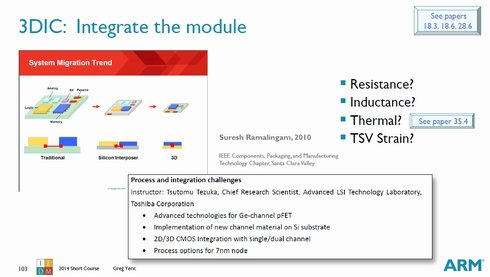

プロセスの異なる複数の半導体チップを使ったモジュールを小型化する時は、基板の配線密度を高めることを考える。標準的な手段は、シリコン配線基板(「インターポーザー」と呼ぶことが多い)の採用である。樹脂基板であるプリント基板の配線ピッチは200μm前後。これに対し、シリコン基板の配線ピッチは容易に1μm未満にできる。半導体チップの入出力信号数にもよるが、シリコン基板の採用によって基板の面積をプリント配線基板の半分以下にすることは決して難しくない。

モジュールをさらに小さくする手法もある。シリコン配線基板(インターポーザ)の上にシリコンダイを積層する技術を使う。例えばインターポーザーの上にロジックのダイを置き、その上にメモリのダイを重ねる。あるいは、インターポーザーの上にアナログのダイを置き、その上に高周波(RF)のダイを重ねる。こうすると、シリコン基板(インターポーザー)の面積をさらに小さくできる。

ここで重要なことは、シリコンダイには手を加えていないことだ。シリコンダイの製造技術は変わっていない。同じ世代の製造技術のままで、システムを小型化している。単位面積当たりのトランジスタ数を増やしているとも言える。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 最新ノートPC5機種を分解 新旧MacBook Proの中身の違いは?

- 「装置は動くがプロセスが成立しない」――He供給危機とナフサ不足の本質

- He/ナフサ供給危機で工場新設も遅延? 装置/チップメーカーへの波及経路を探る

- Apple新CEOはエンジニア出身 製品開発重視への回帰か

- ローム・東芝・三菱電機のパワー半導体はどうなるか

- ルネサス26年1Qは増収増益 車載/AI好調で「足元は当面強い」

- 「Rapidusの隣」に光電融合パッケージ開発拠点、28年度の完成目指す

- 「3社のパワー半導体事業を切り出し合弁設立したい」三菱電機社長