ARMから見た7nm CMOS時代のCPU設計(19)〜微細化なしで小型化を達成する3次元技術:福田昭のデバイス通信(30)(2/2 ページ)

回路を形成したウエハー同士を貼り合わせる

シリコンダイ・レベルでの積層をウエハー全体にまで拡大する手法もある。異なるプロセスで製造した2枚のウエハーの、回路側同士を貼り合わせるのだ。張り合わせた後でウエハーの片方は取り除く。このようにして異なるプロセスで作成した回路を積層する。

2枚のウエハーを貼り合わせる手法は、シリコンダイを積み重ねる手法に比べるとシリコンの量産規模を大きくしやすい。ただし欠点もある。互いに接続する回路面は、貼り合わせ(圧着)のダメージに強い太めの金属配線層になる。高密度な金属配線層(下層の金属配線層)同士を接続することには向かない。

数多くのシリコンダイやシリコン集積回路層などを積層していくと、ダイ間または層間の配線接続が問題になる。入出力信号の構成が単純なメモリ回路は、ワイヤボンディングやフリップチップなどの従来の後工程技術によってシリコンダイ同士を接続しやすい。しかしロジックやアナログなどでは、このような手法は使いづらい。

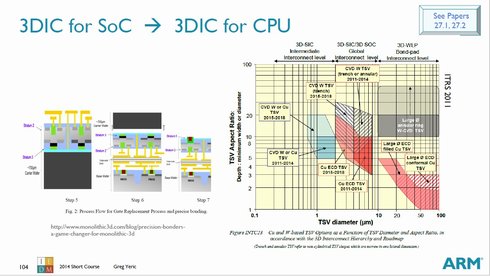

そこで考えられているのが、積層済みの回路層を垂直に貫く孔(あな)を形成し、孔を金属で金属で埋めることによって各回路層を接続する手法である。「シリコン貫通ビア(TSV:Through Silicon Via)」と呼ばれている。孔を埋め込む金属は銅(Cu)あるいはタングステン(W)である。

TSVの直径は100μmと比較的太いものから、1μmと極めて細いものまで、さまざまなタイプが研究されてきた。TSVの直径は重要なファクタだが、深さが劣らず重要なファクタである。直径と深さの比率(アスペクト比)がTSV形成の難しさを示す。

モノリシックな3次元シリコンダイ

2枚のウエハーを貼り合わせる手法は、貼り合わせの回数を増やすことで回路の層数を増やせる。貼り合わせの時に回路面同士ではなく、回路面とウエハー裏面を接続する。これを繰り返すと、積層する回路層の数を増やせる。

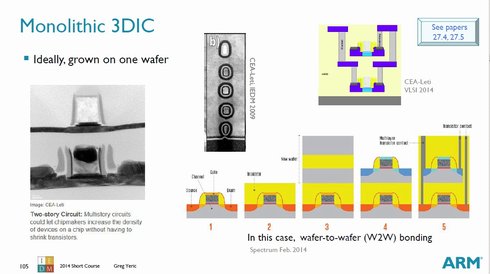

1枚のウエハーにモノリシックに複数の回路層を積層する手法もある。回路層の積層を繰り返すと、トランジスタを微細化することなしに、回路の集積密度を高められる。

これらの手法はいずれも、微細化に頼らずに回路の集積密度を向上させている。微細化が限界に突き当たった時に回路密度を向上する手法の候補でもある。

(次回に続く)

- AI/HPCシステムの死命を制する消費電力・放熱設計(前編)

- AI/HPCシステムのメモリ/ストレージ階層とHBMの高性能化

- ミニダイ(チップレット)間接続におけるSTCO

- 先進パッケージのシステム・製造協調最適化(STCO)

- インターポーザに複数のシリコンダイを近接して並べる2.5次元集積化

- 複数のミニダイ(チップレット)を1つのパッケージに収容する

- モノリシック集積の限界を超えるヘテロジニアス集積化

- AIサーバの高性能化に不可欠となった先進パッケージング技術

- 創刊前の20年間(1985年〜2005年)で最も驚いたこと:「高輝度青色発光ダイオード」(後編)

- 創刊前の20年間(1985年〜2005年)で最も驚いたこと:「高輝度青色発光ダイオード」(前編)

関連記事

次世代3次元SoCは、TSVを使わない――Qualcomm

次世代3次元SoCは、TSVを使わない――Qualcomm

Qualcommは、米国で開催された「International Symposium on Physical Design(ISPD)」で、同社の3次元SoCの技術動向について語った。TSV(シリコン貫通ビア)を使わずに積層することで、小型化と歩留まりの向上を実現したいという。 CMOSイメージセンサーが引っ張る3次元積層技術

CMOSイメージセンサーが引っ張る3次元積層技術

チップを積層し、TSV(シリコン貫通電極)などで接続する3次元IC技術。CMOSイメージセンサーでも、3次元化が進んでいる。 東芝、3次元NAND「BiCS」の製品化を発表――サムスン上回る48層構造

東芝、3次元NAND「BiCS」の製品化を発表――サムスン上回る48層構造

東芝は2015年3月26日、「BiCS」と呼ぶ3次元積層構造を用いたNAND型フラッシュメモリ(以下、3D NAND)を開発し、同日サンプル出荷を開始したと発表した。 3Dプリンタで100nmオーダーの加工が可能に? エバネッセント光を使う微細加工

3Dプリンタで100nmオーダーの加工が可能に? エバネッセント光を使う微細加工

東京大学 先端科学技術研究センターの高橋研究室は、100nmオーダーの分解能で高速に3次元造形を行う技術開発に取り組んでいる。樹脂の硬化にエバネッセント光を使うことで、このような分解能の実現が可能だという。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- イラン戦争の長期化が半導体業界に及ぼす深刻な影響

- 東芝との協議やデンソー提案への対応、ロームが新声明

- NVIDIA製GPU搭載サーバのコスト/スペックを分析してみた

- IBMとLamが「サブ1nmチップ」で協業 高NA EUV導入加速へ

- 「これまでにないダイナミックレンジ」 ソニーのLOFIC画素4Kセンサー

- Micron、PSMCの300mm工場買収完了 第2工場も建設へ

- 全固体二次電池の「200℃動作」を実演、日本電気硝子

- AIの競争軸は半導体から電力へ――日本の戦略の「死角」に

- 「世界初」酸化ガリウムをSi基板にエピ成長、名大ら

- ロームとデンソー、東芝、三菱電機……国内パワー半導体再編の行方