「ムーアの法則」継続の鍵となるか、Si/III-V族の“ハイブリッド”ナノワイヤ:プロセス技術(1/2 ページ)

IBM研究所が、Si(シリコン)とIII-V族化合物半導体を組み合わせたナノワイヤを形成する技術を発表した。独自の「TASE(Template-Assisted Selective Epitaxy)」という技術を使って形成する。TASEで作成したInAs(インジウムヒ素)のナノワイヤは、5400cm2/Vsの電子移動度を達成したという。「ムーアの法則」を継続させる鍵になるかもしれない。

「ムーアの法則」が再び勢いづく可能性がある。SOI(シリコン・オン・インシュレータ)基板のトランジスタチャネルなどに適した、III-V族化合物半導体ナノワイヤの形成が鍵になりそうだ。スイスのチューリッヒと米国ニューヨーク州ヨークタウンハイツに拠点を置くIBM Researchが発表した。

IBMは、独自の「TASE(Template-Assisted Selective Epitaxy)」と呼ばれる技術を用いて、ナノスケールのホール構造やマルチゲートFET(MuG-FET)を製造したという。

IBMの2つの研究拠点が協力したこの取り組みは、Intelを含め、世界中の半導体メーカーが長年開発してきたことを実現したようだ。

IBMは、Applied Physics Lettersで発表した論文の中で、Si(シリコン)とIII-V族化合物半導体*)間の結晶格子の不整合を取り除く技術や、TASEの開発における初期段階の取り組みなどを引用している。結晶格子の不整合を取り除く技術は、他の研究機関が一部、成功しているものだ。

*)InAs(インジウムヒ素)、InGaAs(インジウムガリウムヒ素)、GaAs(ガリウムヒ素)

ナノワイヤ形成のステップ

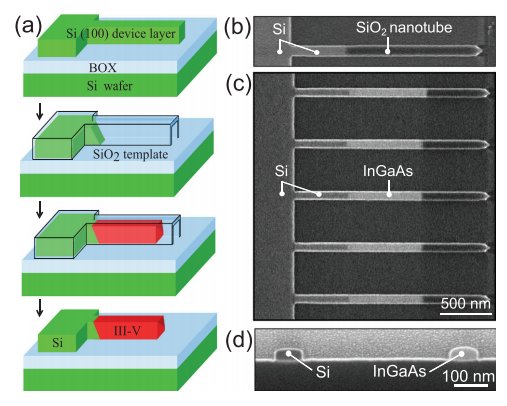

TASEによるナノワイヤ形成のステップは、以下の図の(a)に示されている。

まず、SOI基板上に、Siでナノワイヤを形成する。その上に、SiO2層をALD(原子層堆積)で形成。このSiO2層の中に残っているSiナノワイヤの端をエッチングで切り取る。ここに、III-V族化合物半導体の結晶を、有機金属気相成長法を用いて成長させる。最後に、SiO2層を除去する。そうすると、一番下のように、SiとIII-V化合物半導体を組み合わせたナノワイヤができる。(b)〜(d)は、作成したナノワイヤの電子顕微鏡写真だ。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

「TASE」によるSi/III-Vナノワイヤ 出典:IBM Researchの論文

「TASE」によるSi/III-Vナノワイヤ 出典:IBM Researchの論文