EE Times Japan >

プロセス技術 >

「ムーアの法則」継続の鍵となるか、Si/III-V族の“ハイブリッド”ナノワイヤ:プロセス技術(2/2 ページ)

» 2015年06月12日 12時15分 公開

[R Colin Johnson,EE Times]

電子移動度は5400cm2/Vs

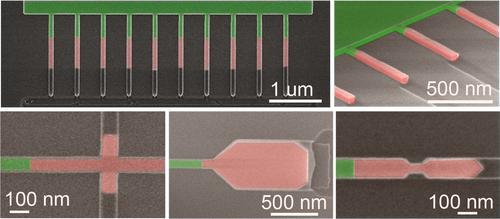

IBMは、「Si/III-V族化合物半導体を使ったハイブリッドなトランジスタを製造するために必要となる、複雑な構造を初めて形成した」としている。具体的には、ナノワイヤの交差接合や、3次元積層のナノワイヤなどだ。IBM Researchの上席研究員で、今回の論文の首席執筆者でもあるHeinz Schmid氏は、「今回の研究成果は、小型化と低コスト化、性能の向上が求められる次世代のコンピュータチップを製造する上で、重要なステップになる」と強調した。

論文によれば、TASEで形成したInAsナノワイヤの交差接合点でホール効果を測定したところ、電子移動度は5400cm2/Vsを実現したという。同時に形成したInAs MuG-FET(幅55nm、厚さ23nm、チャネル長390nm)は、660μA/μmのオン電流と、最大で1.0mS/μm(VDSが0.5V時)のトランスコンダクタンスを示したという。

Schmid氏は論文で、「TASEは、SiとIII-V化合物半導体の統合に向けて強固な土台を築いた」と主張している。

【翻訳:青山麻由子、編集:EE Times Japan】

「EE Times Japan『プロセス技術』」バックナンバー

- ソニーセミコンとTSMC、次世代イメージセンサーで提携 フィジカルAI分野に照準

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

- ソニーとTSMCが新たな合弁検討、半導体のファブライト化とフィジカルAI見据え

- ソニーセミコンとTSMCが合弁会社設立を検討

- MetaとAWSが提携 エージェント型AI強化に最新のArmベースチップ「Graviton5」を大量採用

- 560億ドル投資でも「需要に追い付けない」 AI急成長でTSMC表明

- 経産省、Rapidusに6315億円追加支援 「国益のため必ず成功」

- 先端半導体用フォトレジスト技術棟を新設、3つの機能を集約

- Intel、イーロン・マスク氏の「Terafab」構想に参画 次世代AIチップ生産を支援

- Arm Cortex-M33コア搭載の低価格マイコン、ST

関連記事

Intelの10nmチップ、鍵はIII-V族半導体と量子井戸構造か

Intelの10nmチップ、鍵はIII-V族半導体と量子井戸構造か

Intelは10年近くにわたり、量子井戸電界効果トランジスタ(QWFET)の研究を進めてきた。ある半導体アナリストは、Intelの10nmチップは、III-V族半導体、具体的にはInGaAs(インジウム・ガリウム・ヒ素)とGe(ゲルマニウム)を用いたQWFETになると予測している。 豊橋技科大がシリコン基板にIII-V素子を集積、発光素子の統合が可能に

豊橋技科大がシリコン基板にIII-V素子を集積、発光素子の統合が可能に

豊橋技術科学大学の研究者は、Si(シリコン)基板上にGaN(窒化ガリウム)発光素子やその他の光学材料を集積することに成功したと発表した。 IBM、実用的な量子コンピュータに近づく成果

IBM、実用的な量子コンピュータに近づく成果

IBMは、量子ビット数を拡張できる量子コンピューティング アーキテクチャを開発したという。量子コンピュータ実現に向けた大きな課題であるビット反転エラー/フェーズ反転エラーを補正できる冗長性を持たせたアーキテクチャで、規模を拡大させやすいとする。 IBMのスパコン、ガン治療費の削減に光明

IBMのスパコン、ガン治療費の削減に光明

陽子線をガン細胞に照射して死滅させる陽子線治療。ガンの最先端治療として期待されているが、費用が高額で、照射ポイントの決定に時間がかかるのがデメリットとなっている。IBMの基礎研究所は、スーパーコンピュータを利用することで、陽子線治療の費用を下げられると提案する。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

Special SitePR

あなたにおすすめの記事PR

Si/III-Vナノワイヤの電子顕微鏡写真 出典:IBM Research

Si/III-Vナノワイヤの電子顕微鏡写真 出典:IBM Research