IBMが7nm試作チップを発表、Intelに迫る勢い:EUVとSiGeチャネルで(2/3 ページ)

IBMの3つの成果

IBMが7nm試作チップの製造に成功した背景には、同社が成し遂げた3つの成果がある。EUVリソグラフィ技術を使用したこと、バルクシリコンウエハーに、歪みSiGeトランジスタチャネルを形成したこと、寄生容量の最小化に向けてMOL(中間工程)とBEOL(後工程)の最適化を行ったことだ。これにより、7nmチップ製造工場にプロセスを移管して、同チップを生産できるようになるという。なお、7nmチップ製造工場は、GLOBALFOUNDRIESとSamsungがそれぞれ少なくとも60億〜100億米ドルを投じて建設する計画である。

IBM Researchの半導体技術部門でバイスプレジデントを務めるMukesh Khare氏は、EE Timesに対して、「われわれが試作したチップは、Powerシリーズの性能を向上させるために必要な全ての機能を搭載している。FinFET、SRAMセル、インターコネクトなど7nm Powerプロセッサの実際の製造に必要な技術を搭載し、飛躍的な性能向上を実現した」と語った。

10nmプロセスの開発計画も続行

IBMは、10nm Powerプロセッサの発売計画も続行する。同プロセッサの設計については「2014 International Symposium on VLSI Technology and Applications,(VLAI-TSA)」で発表されたが、市場投入は2016年になるとみられている。さらに、2018年には7nmチップが投入される。「ムーアの法則」は続いていくことになる。

Khare氏は、「7nmチップの生産を委託するまでに、改善すべき点はたくさんあるが、これまでの成果には非常に満足している。われわれは、リソグラフィや材料技術に大きな変革をもたらすことに成功し、クラウドコンピューティングやビッグデータに対応すべく、IBMの高性能システムを進化させられると確信した」と述べている。

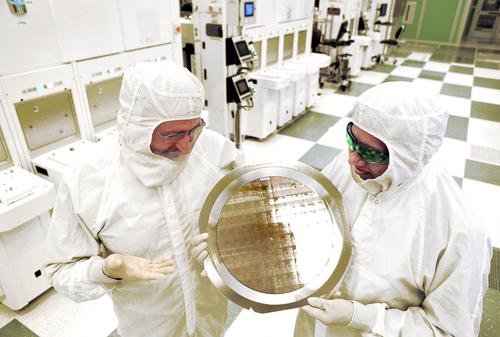

CNSEのMichael Liehr教授(左)と、IBM ResearchのBala Haran氏。7nm試作チップのウエハーを持っている 出典:Darryl Bautista/Feature Photo Service for IBM

CNSEのMichael Liehr教授(左)と、IBM ResearchのBala Haran氏。7nm試作チップのウエハーを持っている 出典:Darryl Bautista/Feature Photo Service for IBM7nm試作チップを発表したことで、GLOBALFOUNDRIESやSamsung、両社に部品を提供するメーカーの共同開発アライアンスにも支持が集まる結果となった。GLOBALFOUNDRIESは、SUNYのIBM研究室から高速道路で30分と立地に恵まれている。また、Samsungは、7nm技術の詳細に通じていることで同技術に関する信頼性を高めた。

米国の市場調査会社であるEnvisioneering Groupでリサーチディレクタを務めるRichard Doherty氏は、同技術の発表前にEE Timesが行った取材で、「IBMとGLOBALFOUNDRIES、Samsungにとって、SUNYと7nmプロセス技術を共同開発したことは正解だった。IBMは、自社工場を持たなくても微細化を進められることを証明するとともに、ムーアの法則を継続できる可能性を提供した。半導体の次期フェーズは、Intelにとっては特に、これまでとはまったく違ったものになるだろう。IBMの“秘伝技術”とも言えるSiGeチャネルは、10nmプロセスで驚くような成果を上げるかもしれないが、7nmプロセスではさらに驚異的な成果が期待できる」と述べた。

Khare氏によると、競合他社も7nmプロセスの試作チップの製造を手掛けているが、微細化によって性能が劣化したことから、沈黙を守っているという。しかし、IBMは同プロセスの各フェーズの最適化に全力を尽くした結果、ムーアの法則に期待される性能の向上を実現できる可能性を見いだした。IBMの7nm FinFETプロセス技術は、30nm以下のピッチで積層してパッケージングすることでチップサイズを約半分にまで縮小した他、消費電力を少なくとも50%低減、性能を50%向上させたという。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増