起業家精神で技術革新――中村修二氏も登壇:CDNLive Japan 2015リポート(1/3 ページ)

日本ケイデンス・デザイン・システムズは、顧客向け技術コンファレンス「CDNLive Japan 2015」を横浜で開催した。日本のユーザーら約900人が参加。基調講演セッションでは、米国本社CEOやノーベル物理学賞受賞者の中村修二氏らが講演を行った。

EDAツール大手ベンダーの日本ケイデンス・デザイン・システムズは2015年7月17日、横浜の横浜ベイホテル東急で、顧客向け技術コンファレンス「CDNLive Japan 2015」を開催した。基調講演セッションでは、米国Cadence Design Systemsの社長兼CEOによる講演や、2014年度ノーベル物理学賞受賞者の中村修二氏による招待講演などが行われた。5つに分かれたテクニカルトラックでは、ユーザーが設計事例などを発表した。本稿では、両氏の講演についてその概要を紹介する。

Cadence Design Systemsの社長兼CEOを務めるLip-Bu Tan氏は、「Innovation in System Design Enablement〜システムデザイン・イネーブルメントにおける革新〜」と題して講演。自動車のADAS(先進運転支援システム)などを事例に挙げ、半導体デバイスの高機能/高性能化がスマートなシステムの実現につながっていくことを示した。

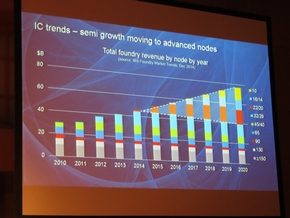

その上で、半導体業界のトレンドや課題などについて触れた。プロセス技術は22/20nmノードから16/14nmノードへ、さらには10nmやその先へと微細化が進展する。特に、「グラフィックプロセッサやイメージセンシングといった用途が、プロセスの微細化をけん引することになろう」と話した。

Cadence Design Systemsの社長兼CEOを務めるLip-Bu Tan氏(左)と、プロセスノード別に見た半導体需要の予測 (クリックで拡大) 出典:日本ケイデンス・デザイン・システムズ、IBS

Cadence Design Systemsの社長兼CEOを務めるLip-Bu Tan氏(左)と、プロセスノード別に見た半導体需要の予測 (クリックで拡大) 出典:日本ケイデンス・デザイン・システムズ、IBSこうした中で、最先端LSIの設計/製造には、トリプルパターニング設計やEUVリソグラフィといった、新たな技術の導入が進む見通しだ。当然ながらLSIの設計はより複雑となり、併せてLSIの機能/動作検証や関連ソフトウェアの開発も難易度が高まることになる。SoCに搭載されるIPコア数も格段に増加する。Tan氏は、「16/14nmノードのSoCの中には、123個のIPブロックが搭載されているチップもある」と述べた。

続いて、システム開発のトレンドや課題について語った。例えば2.5次元や3次元実装できるパッケージ技術の適用や、フレキシブル基板への対応、ファームウェアやドライバソフトウェアなどに対する開発負荷の増大、システムでの消費電力を低減するシミュレーション技術の活用などを挙げた。これらのトレンドに対して、システム開発にはIP/ICベンダーからソフトウェアベンダーまで、垂直統合の開発体制が不可欠だという。

Cadence Design Systemsでもこうした動きに対して、新たなIPコアや検証ツールベンダーの買収などを行い、設計環境の統合化を進めている。さらに、「起業家精神に基づきイノベーションを続けている」という。スタンフォード大学との共同研究など、さまざまな大学との先端研究も積極的に行っていく考えである。

次世代技術への対応に関してはパートナー企業との協業にも力を入れる。「TSMCやARMなどとの協力関係を深めていくことで、先進の設計ツールにおいても業界のリーダー的立場を維持していく」方針を示した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- NVIDIAとメモリ3社、世界半導体売上高の42%占める

- 「Renesas 365」がついに始動 「不可能だった規模」の検証、数分で

- デンソー、ロームに対する株式取得提案を正式表明

- もはや半導体メーカーの域を超えた NVIDIA最新エッジ機器を分解

- Armが半導体の自社開発に参入、AIデータセンター向けCPU発表

- キオクシアがNanyaに774億円出資、DRAM長期供給契約を締結

- 魚津はTower、砺波はNuvotonに TPSCo事業の再編を発表

- イラン戦争の長期化が半導体業界に及ぼす深刻な影響

- パワー半導体再編が本格化 ローム・東芝・三菱電機が協議開始へ

- 次世代パワー半導体 「期待の5材料」の現在地――電子版2026年3月号