EE Times Japan >

プロセス技術 >

抵抗変化メモリとGaNデバイス:福田昭のデバイス通信 IEDM 2015プレビュー(4)(2/3 ページ)

» 2015年11月10日 09時30分 公開

[福田昭,EE Times Japan]

InGaAs FETとSiGe FETをモノリシック積層したCMOS回路

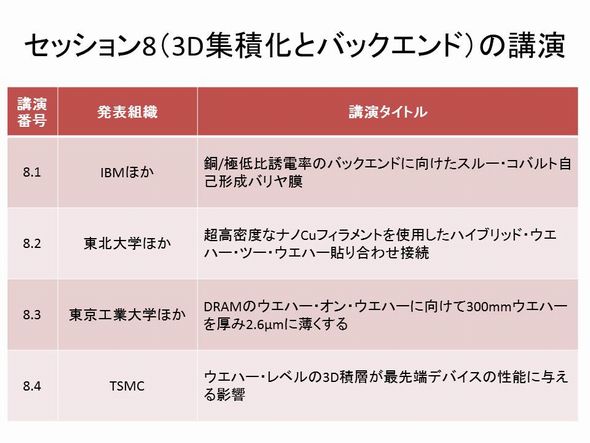

セッション8(プロセス技術と製造技術)のテーマは「3D集積化とバックエンド」である。かつては3次元(3D)集積回路の製造技術ではウエハーの貼り合わせが主流だった。今回は、ウエハー貼り合わせ技術に加え、モノリシックに3次元(3D)の集積回路を実現しようとする試みが目立つ。

東北大学とXilinxの共同研究グループは、Cuフィラメントと異方性導電フィルムを利用した高密度かつ多ピンのウエハー貼り合わせ技術を報告する(講演番号8.2)。熱圧着のウエハー貼り合わせによって直径3μmのCu電極を13万6800本、形成した。

東京工業大学とディスコの共同研究チームは、2Gビット DRAMを形成した300mmウエハーを2.6μmまで薄くする技術を開発した(講演番号8.3)。ウエハーを薄くしていったときに、厚みが5.6μmまではDRAMの電荷保持特性で劣化はまったく見られなかった。厚みが2.6μmのときは、電荷保持特性が劣化した。

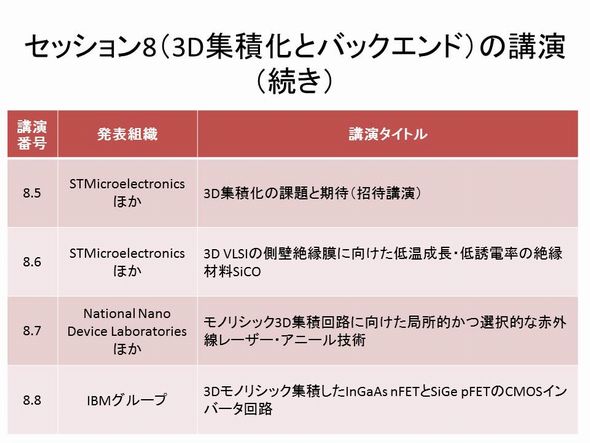

ドイツのIBM Researchと米国のIBM T.J. Watson Research Centerは、絶縁基板の上にInGaAs nチャンネルFETとSiGe pチャンネルFETをモノリシック積層した3次元のCMOS回路を製造した結果を共同で発表する(講演番号8.8)。トップ層がInGaAs、ボトム層がSiGeである。トップ層の形成によってボトム層のトランジスタ性能は劣化していない。CMOSインバータを試作して電源電圧0.25Vで動作を確認した。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- 「膿み出し切った」SiC関連減損で過去最大1584億円赤字 ローム

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- パワー半導体3社連合とデンソー提携のアナログ「両軸を強化」 ローム社長

- 26年3月の世界半導体市場は79%増、日本も10カ月ぶりプラス成長

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- DRAM不足で変わるAIシステム設計 エッジAIや特化型モデルに追い風

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

Special SitePR

あなたにおすすめの記事PR