ルネサス、自動運転車向けSoC用高速SRAMを開発:16nm FinFETに最適化したデュアルポート型

ルネサス エレクトロニクスは2015年12月9日、16nm世代以降の先端プロセスを採用する車載情報機器用SoC(System on Chip)に内蔵するための高速SRAMを開発したと発表した。

ルネサス エレクトロニクスは2015年12月9日、16nm世代以降の先端プロセスを採用する車載情報機器用SoC(System on Chip)に内蔵するための高速SRAMを開発したと発表した。0.7Vの低電圧動作条件で、688ピコ秒の高速動作を試作SoCで実証した。自動運転を実現するための、リアルタイム画像処理の画像バッファメモリとして、車載情報機器用SoC製品に展開していく方針。

開発したSRAMは、デュアルポートタイプと呼ばれる同時に読み出しと書き込みが行えるタイプのメモリ。一般的なシングルポートSRAMに比べ約2倍のメモリアクセス性能を実現できる。ただ、シングルポートタイプに比べ、チップサイズが大きくなる他、アクセス速度向上に伴う消費電力の増大、動作下限電圧マージンの悪化などを招く。

そうした中で、ルネサスは、16nm世代の以降のプロセスで主流のFinFET構造に最適化したデュアルポートSRAM用メモリセル構造を開発。さらにシングルポートSRAM向けに開発したワード線ブースト型アシスト回路技術を応用し、低電圧でも安定して高速読み出し/書き込み動作が行え、小さなサイズで消費電力を抑えたSRAMを実現したという。

688ps動作、3.6Mbit/mm2を達成

ワード線ブースト型アシスト回路とは、デバイス素子のバラツキに起因する下限動作電圧マージンの悪化に対応する技術。一般的に読み出し時の動作を安定させるため、アクセス時にワード線の電圧をわずかに下げるが、その場合、書き込み時の動作マージンが悪化し、読み出し速度が低下した。それに対し、ワード線ブースト型アシスト回路技術は、FinFET構造の特徴を生かし、ワード線電圧をわずかに上げて、読み出し時と書き込み時でパルス幅を変えるというもの。今回、新たにデュアルポートSRAMに適用することで、0.7Vの低電圧動作でも688ピコ秒という高速動作を16nm FinFETプロセスでの試作で実現した。

チップ面積の低減に関しては、いくつかあるデュアルポートビットセルタイプの中から、FinFETに最適なレイアウト対称性に優れ、28nm世代まで用いたメモリセルと異なるメモリセルタイプを選択。その結果、1mm2当たり3.6Mビットという高集積化を実現したとする。

R-Carへ展開か

今回開発した技術については、米国ワシントンで開催されている最先端電子デバイスの国際学会「IEDM 2015」で2015年12月8日(米国時間)に発表されている。

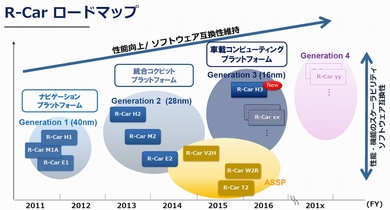

ルネサスは2015年12月2日に、車載情報機器用SoC「R-Carファミリ」として台湾TSMCの16nm FinFET+プロセスを用いた新世代品「R-Car H3」のサンプル出荷を開始している*)。今回開発したSRAMについても、R-Carファミリに展開される見込み。

*)関連記事:ルネサス 自動運転車の頭脳となる次世代SoC発表

関連記事

ルネサス 自動運転車の頭脳となる次世代SoC発表

ルネサス 自動運転車の頭脳となる次世代SoC発表

ルネサス エレクトロニクスは2015年12月2日、車載情報システム向けSoC「R-Carシリーズ」の第3世代品を発表した。2018年以降に市販される自動車への搭載を見込んだ製品群。第1弾製品として同日、サンプル出荷を開始した「R-Car H3」は“自動運転時代のSoC”と位置付けたハイエンド品で、最先端となるTSMCの16nm世代FinFET+プロセスを採用し、高性能な処理能力を盛り込んだ。 ルネサスが競合とも手を取り、開発を進めるCIS

ルネサスが競合とも手を取り、開発を進めるCIS

ルネサス エレクトロニクスは、自動走行技術をテーマに、パートナー各社が連携しCIS(Car Information System:車載情報システム)ソリューションを開発する「R-Carコンソーシアム」の活動報告などを行う定例イベントを開催した。統合コックピットやADAS向けのソリューションが多数紹介されたので、その一部を紹介する。 ルネサスが“クルマ”を売る!? その真意とは

ルネサスが“クルマ”を売る!? その真意とは

ルネサス エレクトロニクスは米国で開催した「DevCon 2015」で、同社のADAS(先進運転支援システム)向けの最新SoCなどを搭載した自動車を披露した。実は、この自動車は、自動運転車などの開発を促進すべく同社が発表した“プラットフォーム”である。 ルネサスの車載情報機器向けSoC、第3世代「R-Car」は16nmプロセス、最大8コアに

ルネサスの車載情報機器向けSoC、第3世代「R-Car」は16nmプロセス、最大8コアに

ルネサス エレクトロニクスはドイツ ミュンヘンで開催中の「electronica 2014」(2014年11月11〜14日)で、車載情報機器向けSoC「R-Car」など車載向け半導体の展示を行うとともに、次世代の「第3世代R-Car」製品に16nmプロセスを採用し、最大8つのCPUコアを搭載する方針を明かした。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ヘリウム調達停止――AIブームを崩壊させる「見えない臨界点」(前編)

- 石炭灰から「レアアース元素」を回収、新日本繊維【訂正あり】

- Rapidus、IIM-1を「世界初の前/後工程一貫工場に」

- ヘリウム調達停止――AIブームを崩壊させる「見えない臨界点」(後編)

- 「27年度後半の2nm量産誓う」 Rapidus、解析センター開設

- EVに吹く逆風 デンソーの焦りとロームが求める勝機とは

- 経産省、Rapidusに6315億円追加支援 「国益のため必ず成功」

- 光電融合チップレットの技術開発を開始 LSTCとimec

- 「技術を束ねて高価値システムに」 デンソーが2030年中計発表

- 京セラ、ウシオ電機の半導体レーザー事業を取得へ