メモリの薄化限界は4μm! 2μm台で劣化を確認:バンプレスTSV技術と併用で配線長1/10も可能に(1/2 ページ)

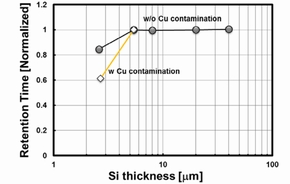

東京工業大学とWOWアライアンスは2015年12月15日、300mmシリコンウエハーの厚さを2μmにすることで、DRAMの特性が劣化することを確認し、シリコンウエハーの薄化は4μm程度が実用的であるとの研究成果を発表した。

テラビット級3D メモリへの応用も

DRAMなど半導体メモリは、記憶密度を高めるためメモリチップを積層する「3次元積層メモリ」(3D メモリ)の開発が進められている。チップを積層した場合の上下配線は、メモリチップ間を接続するバンプサイズと、チップを貫通するビア(TSV:Through Silicon Via)の長さ、すなわちウエハーの厚さで決まる。一般に配線長を短くすることで、配線抵抗と電気容量を小さくでき、消費電力を抑えられるなどの利点がある。

東京工業大学異種機能集積研究センター教授の大場隆之氏とWOWアライアンス*)はこれまでに、バンプを使用せずに、TSVだけでチップ間接続を行うバンプレスTSV配線技術を開発。ウエハーを薄くすることで極限まで上下配線を短くできる技術を確立している。

*)東京工業大学を中心に設計・プロセス・装置・材料半導体関連の複数企業および研究機関からなる研究グループ

そうした中で今回、ウエハーをどこまで薄くできるかの実証を実施。なお、東工大などによると「どこまで(ウエハーを)薄くできるのかはこれまで明らかになっていなかった」とする。

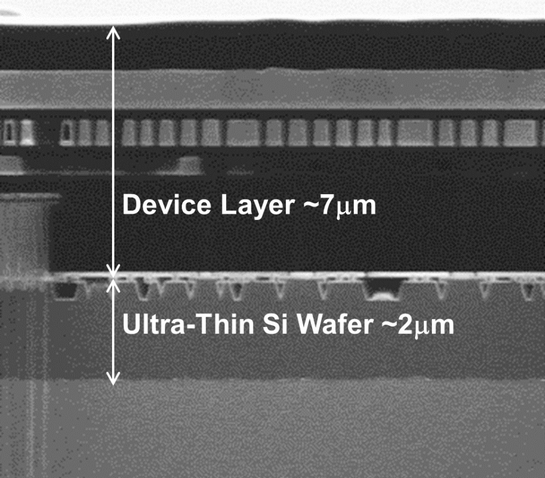

大場氏らは、実証にあたり、2μm台までウエハーの薄化を行った。2μm台の厚さは、デバイス層の3分の1以下の厚さであり、機械研削方式では「世界初の試み」(東工大)となった。ウエハーの薄化は775μm厚の300mmウエハー上に、先端2GビットDRAMを形成した後、機械研削による薄化を実施した。

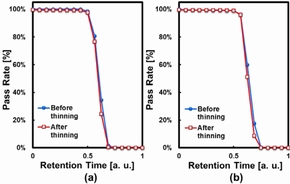

2μm程度まで薄化したところ、デバイス特性に劣化が観察*)され、「DRAMの限界厚さが4μm前後にあることを明らかにした」という。

*)観察箇所の厚さ2.6μmで劣化を観察

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

- パワー停滞も光デバイス堅調、三菱電機の半導体部門

Wafer on Wafer(WOW)プロセスを用いて2μm台まで薄化したDRAMの断面電子顕微鏡写真 出典:東京工業大学

Wafer on Wafer(WOW)プロセスを用いて2μm台まで薄化したDRAMの断面電子顕微鏡写真 出典:東京工業大学