ルネサス 90nm BCDプロセス混載可能なフラッシュ:次世代車載マイコンに適用へ(2/3 ページ)

読み出し時に選択ゲートに正電圧を印加しない

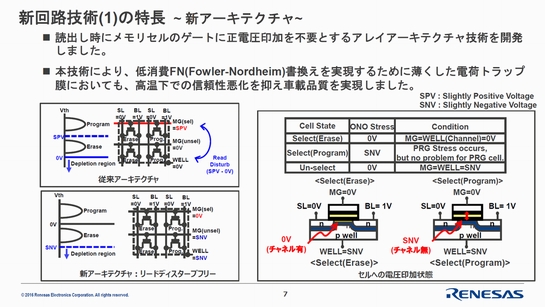

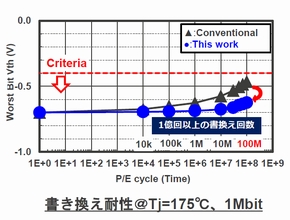

書き換え耐性1億回という信頼性は、主に2つの回路技術で実現した。1つは、読み出し時にメモリセル選択ゲートへの正電圧印加を不要にするアレイアーキテクチャ技術だ。

電荷(チャージ)トラップ方式のフラッシュメモリの場合、FN(Fowler-Nordheim)トンネル効果を利用して絶縁膜(電荷トラップ膜)に挟まれた記憶領域に電荷を出し入れする。小さな電力で、FNトンネル効果を起こすには、電荷トラップ膜を薄くする必要があるが、薄くすると信頼性が悪化する。具体的には、読み出し時に、メモリ選択ゲート(MG)に正電圧を印加する際に生じる電位差が、電荷トラップ膜にストレスを与え、劣化(しきい値電圧が下がる/リードディスターブ)の原因となる。

これに対し、ルネサスのアレイアーキテクチャは、読み出し時にメモリ選択ゲート(MG)に正電圧を印加せず、0Vを与える。代わりに、サブストレート側(WELL)に負電圧を印加することで、読み出しに必要な電位差を作り出す。この場合にも、電荷トラップ膜に電位差が加わることになるが「ほぼ劣化要因とはならなくなった」(ルネサス)とする。

電界の印加を高度に緩和する技術

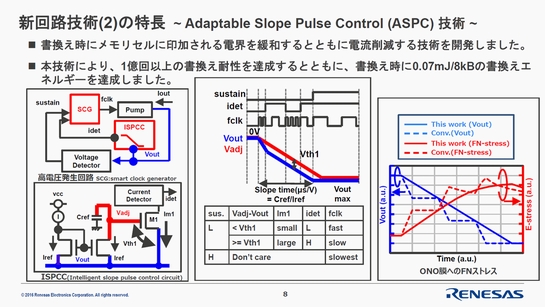

もう1つの信頼性向上技術は、書き換え時にメモリセルに印加される電界を緩和する「Adaptable Slope Pulse Control」(ASPC)技術だ。

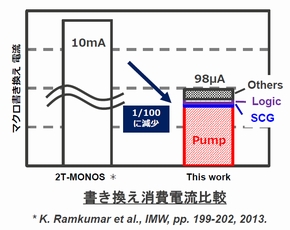

メモリセルは急な電界の変化に弱く、段階的に電界を与え、メモリセルへのストレスを軽減する手法が有効だ。既に、多くのフラッシュメモリで段階的に電界を加える技術が用いられている。「一般的なフラッシュメモリは、数段階の電界切り替えパルス(書き換えパルス)生成でも十分な信頼性を確保できたが、より高い信頼性を得るには、さらにスムーズなパルス生成が必要だった」とし、ルネサスは高速なパルス生成で、なだらかに電界を与えていく回路を構築。また、メモリセルの容量などの状況を検知し、電界の印加を最適化する回路も搭載。同回路により、無駄な電界印加を避け信頼性を高めるとともに、書き換えに必要な消費電流を抑えることに成功。書き換え時の消費電流は98μAで「従来の書き換え電流よりも2桁少ない」(ルネサス)とする。8Kバイト容量のメモリセルの書き換えに必要なエネルギー量は0.07mJ(128Kバイト容量試作チップでの測定結果)を実現している。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増