メモリ・アーキテクチャの基礎:福田昭のデバイス通信 ARMが語る、最先端メモリに対する期待(4)(1/2 ページ)

今回は、NANDフラッシュメモリ登場後のメモリ・アーキテクチャを見ていきながら、「CPUのメモリに対する要求」を考えていく。

NANDフラッシュメモリが新しい階層を生み出した

国際会議「IEDM」のショートコースで英国ARM ReserchのエンジニアRob Aitken氏が、「System Requirements for Memories(システムがメモリに要望する事柄)」と題して講演した内容を紹介するシリーズの第4回である。

前回からは、講演の第2パートである「CPUのメモリに対する要求」の概要をご報告している。前回は、CPUアーキテクチャの変遷を振り返るとともに、NANDフラッシュメモリが登場する以前のメモリ・アーキテクチャを説明した。

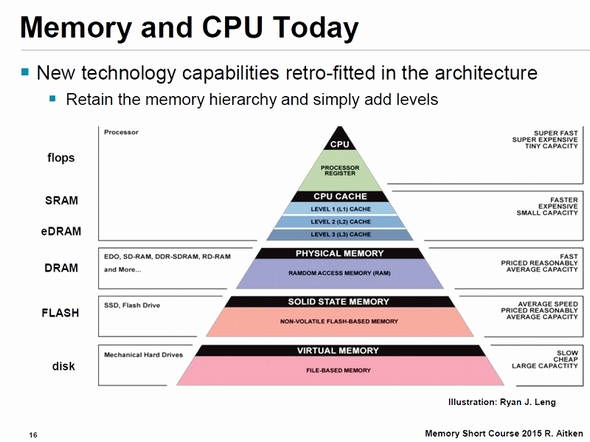

既に述べたように、CPUを搭載したシステムのメモリ・アーキテクチャは、正三角形あるいはピラミッド形をした図形と、水平な階層を垂直方向に積み重ねた構造で説明することが多い。NANDフラッシュメモリが発明されて普及する以前は、ピラミッド図形の頂点(最も高速なメモリ)から底辺(最も記憶容量の大きなメモリ)に向かって、「レジスタ」「キャッシュ」「主記憶」「仮想記憶(ストレージ)」の階層でメモリシステムを構成していた。

NANDフラッシュメモリの発明と普及によってSSD(Solid State Drive)に代表されるフラッシュ・ストレージが登場し、急速に進化していった。SSDの記憶容量は急激に増大し、記憶容量当たりの単価は急激に低下した。その結果、メモリ・アーキテクチャのピラミッド図形には、新しい階層が加わった。「主記憶」と「仮想メモリ」の間に、SSDやUSBメモリなどのフラッシュ・ストレージによる「固体メモリ(Solid State Memory)」の階層が入り始めた。これが現在のメモリ階層である。

揮発性メモリと不揮発性メモリ

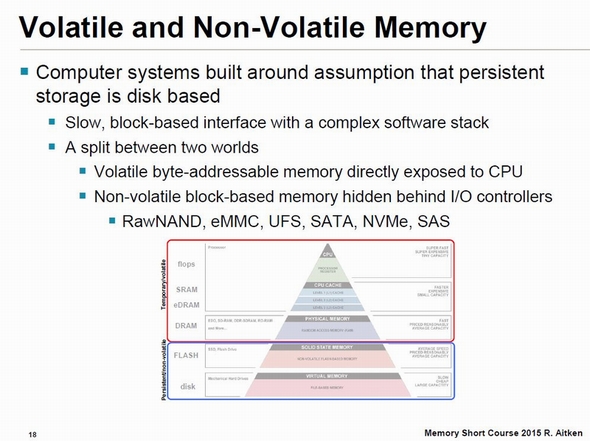

現在のメモリ・アーキテクチャは大きく、2つの世界に分かれている。1つは「揮発性(Volatile)」メモリの世界であり、もう1つは「不揮発性(Non-Volatile)」メモリの世界である。

揮発性メモリとは、電源をオフにすると記憶内容が消えてしまう性質のメモリを指す。メモリ・アーキテクチャのピラミッドでは上部に位置する。「レジスタ」から「主記憶」までの階層だ。CPUがバイト単位で直にアクセス可能なメモリの階層でもある。

不揮発性メモリとは、電源をオフにしても記憶内容が維持される性質のメモリを指す。メモリ・アーキテクチャのピラミッドでは下部の位置する。具体的には、「固体メモリ」と「仮想メモリ」の階層が相当する。

固体メモリと仮想メモリの階層は、CPUが直にアクセスできない。またアクセス単位はバイト単位ではなく、もっと大きな「ブロック」と呼ぶ単位になる。例えば仮想メモリのデバイスであるHDDは、512バイトを1個のブロックとして扱う。

固体メモリと仮想メモリでデータのやりとりを制御するのは、入出力コントローラである。まずCPUと入出力コントローラが通信し、次に入出力コントローラがメモリにデータを書き込んだり、メモリからデータを読み出したりする。CPUから見ると、データへのアクセスは間接的になる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- 「世界2位」は実現するか、ローム、東芝、三菱電機とデンソーの選択は

- Musk氏は「半導体製造の再定義」を目指すのか

- 世界半導体市場は26年2月に大幅成長、日本のみ9カ月連続マイナスに

- ローム、8インチSiC MOSFET開発の技術目標を2年前倒しで達成

- 米Waymoの世界展開は東京から 「開始まで何年もかからない」

- 300mmファブ装置の投資額、2年連続で2桁成長へ

- ヒューマノイドはどこまで現実になっているのか

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- Intelがアイルランド工場を完全子会社化、Apolloから49%買い戻し