メモリ・アーキテクチャの基礎:福田昭のデバイス通信 ARMが語る、最先端メモリに対する期待(4)(2/2 ページ)

» 2016年02月26日 11時30分 公開

[福田昭,EE Times Japan]

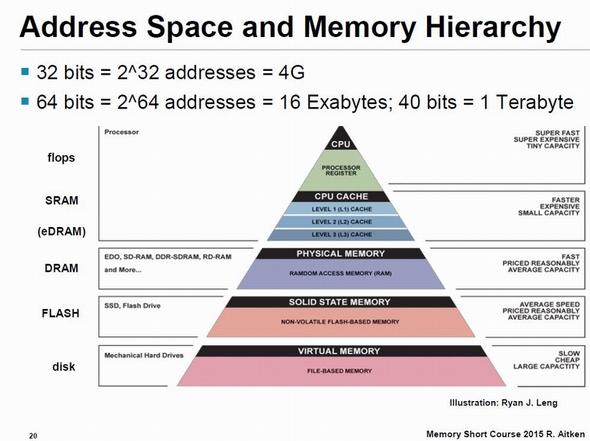

アドレスの幅がメモリ空間の大きさを決める

CPUが直に扱うメモリ空間の大きさ(記憶容量の大きさ)を決めるのは、メモリ・アドレスの幅である。例えば32ビット幅のアドレス(32ビット・アドレス)のCPUが扱うメモリ空間の大きさは、4Gバイト(2の32乗バイト)になる。従って、4Gバイトを超える主記憶(システム・メモリ)を32ビットCPUシステムが搭載しても、4Gバイトを超える部分は直接的には扱えない。CPUが扱えるメモリ空間を拡張する仕組みが必要となる。

一方、64ビット・アドレスのCPUが扱うメモリ空間の大きさは、16エキサバイトにも達する。4Gバイトのおよそ40億倍にもなる膨大な大きさであり、メモリ・アドレスとしては大き過ぎるともいえる。

そこで、現在の64ビット組み込みシステムでは、CPU内部でアドレスの幅を40ビットに狭めることによってメモリ空間を1Tバイトに縮小することが多い。組み込みシステムで1Tバイトを超える主記憶を搭載することは当面、考慮する必要がないからだ。

(次回に続く)

関連記事

3D XPoint、開発から製造へ

3D XPoint、開発から製造へ

IntelとMicron Technologyが開発した「3D XPoint」は、製造の段階へと移る見込みだ。量産には12〜18カ月かかるとみられている。また、3D XPointでは、カルコゲナイド材料と「Ovonyx」スイッチが使われていることが明らかになった。 「ムーアの法則を進める必要がある」――ARM

「ムーアの法則を進める必要がある」――ARM

2015年12月7〜9日に開催された「IEDM 2015」の基調講演で、ARMのシニアリサーチャーであるGreg Yeric氏は、「半導体チップの微細化は一段と困難になっているが、それでもムーアの法則を続ける必要がある」と語った。 3D XPointの製造プロセスは「20nmからスタート」

3D XPointの製造プロセスは「20nmからスタート」

EE Times Japanではこのほど、Intel/Micronが発表した不揮発性メモリ「3D XPoint」に関しての疑問を、両社の広報担当に問い合わせたところ、「20nmのプロセスノードで製造している」との回答を得た。 次世代ストレージ、10個の注目技術

次世代ストレージ、10個の注目技術

3次元DRAMの量産が始まり、相変化メモリ(PCM)、スピン注入磁気メモリ(STT-MRAM)など次世代メモリの技術開発がさかんになっている。ここでは、注目のメモリ技術を10個紹介する。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

Special SitePR

あなたにおすすめの記事PR