CPUアーキテクチャの基礎:福田昭のデバイス通信 ARMが語る、最先端メモリに対する期待(5)(1/2 ページ)

今回から、CPUアーキテクチャとメモリ・システムの関連について掘り下げていこう。まずは5段パイプラインアークテクチャを例に挙げ、メモリ・システムとの関連をみていく。

パイプラインで動作するCPU

国際会議「IEDM」のショートコースで英国ARM Reserch社のエンジニアRob Aitken氏が、「System Requirements for Memories(システムがメモリに要望する事柄)」と題して講演した内容を紹介するシリーズの第5回である。

前々回からは、講演の第2パートである「CPUのメモリに対する要求」の概要をご報告している。今回からは、CPUアーキテクチャとメモリ・システムとの関連に関する基礎的な講演のパートをご紹介していく。

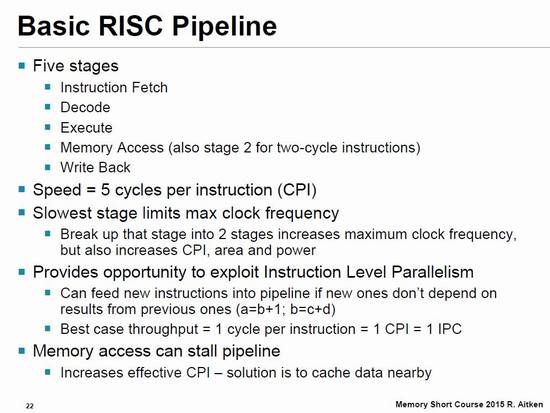

初めはCPUアーキテクチャである。講演では説明を簡単にするために、5段(5ステージ)のパイプラインを備えるRISC型CPUのアーキテクチャを例として挙げた。パイプラインの各段(ステージ)は、「命令フェッチ」「命令デコード」「実行」「メモリアクセス」「ライトバック」の順番に進む。1段を進むのに1クロック・サイクルを必要とするので、このパイプラインは最短時間だと5クロック・サイクルで1命令の実行が完了する。

クロック周波数の最大値を決めるのは、処理時間の最も長い段(ステージ)である。処理時間の長いステージを2つのステージに分割すると、クロック周波数の最大値が向上する。ただし、パイプラインの段数が増えると、1命令の実行が完了するまでのクロック・サイクル数が増加するとともに、シリコン面積と消費電力が増加する。

パイプライン動作とキャッシュアクセス

パイプライン・アーキテクチャの良いところは、「関連のない命令」を連続して実行できることだ。ここで関連のない命令とは、ある命令の実行結果に依存せずに、実行を開始できる命令を指す。5段のパイプラインだと、最大で5つの命令を連続して実行できる。すると実効的には、1個の命令を1クロック・サイクルで処理することになる。

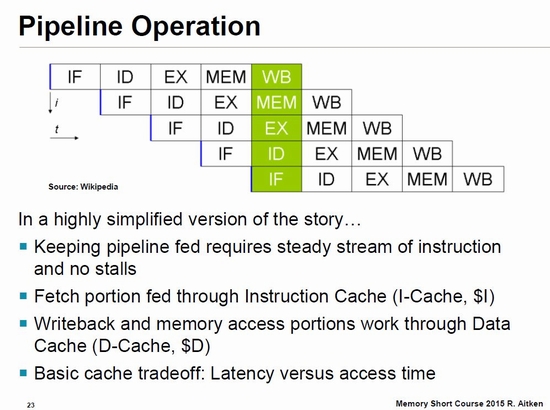

パイプラインの動作は、メモリ・アクセスのふるまいに左右される。場合によっては動作が一時的に停止することもある。このような事態を防ぐために、メモリは実行ユニットのすぐ近くに置く。これがキャッシュである。命令を格納する命令キャッシュと、データを格納するデータキャッシュを用意するのが普通だ。

パイプラインとメモリの関係を、もう少し詳しく見ていこう。命令フェッチ段では、命令キャッシュから、対象の命令を読み込む。メモリアクセス段とライトバック段では、データキャッシュにアクセスする。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- NVIDIAとメモリ3社、世界半導体売上高の42%占める

- 「Renesas 365」がついに始動 「不可能だった規模」の検証、数分で

- デンソー、ロームに対する株式取得提案を正式表明

- Armが半導体の自社開発に参入、AIデータセンター向けCPU発表

- もはや半導体メーカーの域を超えた NVIDIA最新エッジ機器を分解

- キオクシアがNanyaに774億円出資、DRAM長期供給契約を締結

- 魚津はTower、砺波はNuvotonに TPSCo事業の再編を発表

- イラン戦争の長期化が半導体業界に及ぼす深刻な影響

- 次世代パワー半導体 「期待の5材料」の現在地――電子版2026年3月号

- ソニー・ホンダモビリティ、EV「AFEELA」開発中止