SRAMの基本要素とレイアウト:福田昭のデバイス通信 ARMが語る、最先端メモリに対する期待(13)(1/2 ページ)

今回からはSRAMについて知っておくべきことを紹介していく。まずは、多くの半導体メモリにも共通するSRAMシリコンダイの基本レイアウトから説明していこう。

SRAMを構成するいくつかの要素

国際会議「IEDM」のショートコースで英国ARM Reserch社のエンジニアRob Aitken氏が、「System Requirements for Memories(システムがメモリに要望する事柄)」と題して講演した内容を紹介するシリーズの第13回である。

前回までは、DRAMの現状と将来性を解説した。今回からは、SRAMについて知っておくべき事柄を説明しよう。

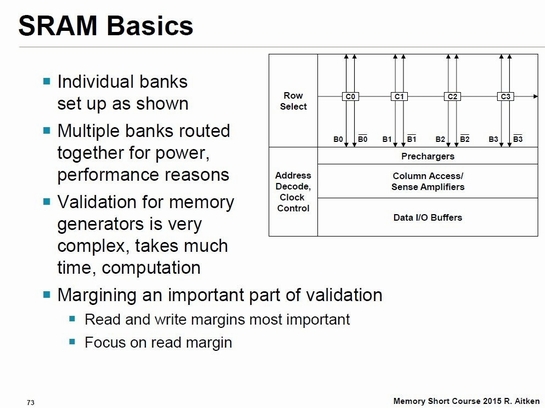

始めに、SRAMシリコンダイの基本レイアウトを示す。この基本レイアウトはSRAMに限らず、多くの半導体メモリで共通なので、非常に大切である。

半導体メモリでデータを記憶する単位素子を「メモリセル」と呼ぶ。普通は1個のメモリセルに1ビットのデータを記憶する。メモリセルを平面の2次元マトリクス状に数多くならべることで、設計仕様である記憶容量を実現する。2次元マトリクス状(あるいは行列状)にメモリセルをならべたものを「メモリセルアレイ」と呼ぶ。

半導体メモリのメモリセルアレイが物理的に1個の行列で構成されることはまずない。通常は「バンク」と呼ぶ複数の行列に分割する。分割する数は2のべき乗で、4バンク、8バンク、16バンクなどがある。複数のバンクに分割するのは、動作の制御や電源の管理などを容易にするためだ。

メモリセルアレイのほかに、SRAMチップには制御や増幅、電源分配、クロック分配などを担う周辺回路(「ペリフェラル」とも呼ぶ)が存在する。周辺回路は、アドレスのデコーダー回路、行(ロウ)と列(カラム)の選択回路、ワード線の駆動回路、センスアンプ回路、プリチャージ回路、クロック回路などで構成される。

さらにはSRAMの外部とデータ信号をやりとりする入出力回路(「IO」「I/O」とも呼ぶ)がある。かつては周辺回路と入出力回路の電源電圧が等しかったので、両者をまとめてペリフェラルと呼称することが少なくなかった。最近は外部インタフェース規格と合わせるために入出力回路の電源電圧を独自に設定することが多い。このため現在は、周辺回路と入出力回路を分けて扱うことが普通になっている。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待