BLE ICの受信感度を4dBm改善したクロック生成器:スプリアスを互いに相殺させて抑制

東芝は2016年6月14日、無線通信ICのクロック信号に起因する妨害波(スプリアス)の発生を抑えて受信感度を改善する「スプリアスキャンセルクロック生成器」を開発したと発表した。

消費電力18μW

東芝は2016年6月14日、無線通信ICのクロック信号に起因する妨害波(スプリアス)の発生を抑えて受信感度を改善する「スプリアスキャンセルクロック生成器」(SCCG: Spur Canceled Clock Generator)を開発したと発表した。

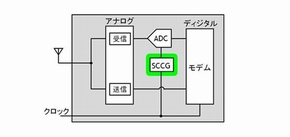

無線通信ICは、アナログ部、デジタル部、A-Dコンバーターなどのミックスドシグナル部が同一チップ上に混載され、A-Dコンバーターやデジタル回路の基準信号となるクロック信号の高調波の一部がスプリアスとなり、受信感度を劣化させていた。従来技術では、受信感度を改善する回路設計により、消費電力やチップ面積、開発コストが増大するといった課題があるという。

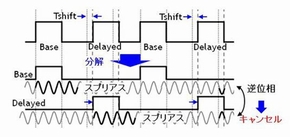

同クロック生成器は、生成されるクロック信号の一部のタイミングを遅らせることで、ある位相のスプリアスと逆の位相のスプリアスを同時に発生させ、スプリアスを互いに相殺させることでスプリアスの発生を抑えるという。消費電力は18μW、占有面積は40μ×120μmである。これにより、「無線通信ICの消費電力、チップ面積をほぼ増加させずにスプリアスの発生を抑えることができる」(東芝)と語る。

同技術をBluetooth Smart ICに適用することで、スプリアスにより劣化した受信感度が4dB改善し、−93dBmの受信感度を全てのチャンネルで実現。同社は、2016年度上期中に同技術を搭載したBluetooth Smart向けLSIを発売する予定としている。

なお、今回の開発成果については、米国ホノルルで開催された半導体デバイスに関する国際会議「VLSI技術シンポジウム2016」で、その詳細が発表された。

関連記事

ルネサス「世界最速/高集積」の画像処理用SRAM

ルネサス「世界最速/高集積」の画像処理用SRAM

ルネサス エレクトロニクスは2016年6月16日、16nm以降のFinFETプロセスを用いたSoCに内蔵するためのSRAM技術として、「世界最高の集積性と速度を実現したSRAMを開発した」と発表した。 あらゆる信号発生機能を持ち運び可能な1台に集約

あらゆる信号発生機能を持ち運び可能な1台に集約

テクトロニクスは2016年5月、従来のファンクションジェネレーターと、デジタル出力対応任意波形ジェネレーターの機能を1台に集約した信号発生器「AWG4000シリーズ」を発表した。 ハイレゾ音源を極める“15万円の水晶発振器”に迫る

ハイレゾ音源を極める“15万円の水晶発振器”に迫る

日本電波工業がこのほどサンプル出荷を開始した水晶発振器「DuCULoN」(デュカロン)。デジタルオーディオ音源を忠実に再現させるため、技術の粋を集め測定限界まで位相雑音を減らしたという1個15万円という異色の水晶デバイスに迫った。 有線通信編:40Gビット/秒の超高速伝送を実現する回路技術

有線通信編:40Gビット/秒の超高速伝送を実現する回路技術

無線、有線ともに、通信技術への関心は高い。今回は、第6回の無線通信技術に続き、有線通信の注目講演を紹介する。具体的には、低消費電力の10Gビット/秒シリアルリンクや、シリコンフォトニクス技術による高速トランシーバなどがある。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

- パワー停滞も光デバイス堅調、三菱電機の半導体部門