FinFETサイズの物理的な限界は?:「ITF 2016」で語られた半導体の未来(3)(1/2 ページ)

ベルギーで開催された「IMEC Technology Forum(ITF) 2016」では、2.5D(2.5次元)のチップ積層技術や、FinFETのサイズの物理的な限界についても触れられた。

2.5Dの積層技術

前回、EUV(極端紫外線)リソグラフィー技術は、半導体プロセス微細化の“万能策”ではないという話をした。

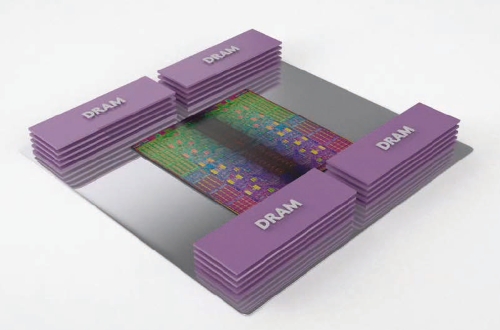

パッケージング、特にチップや回路を積層する新しい方法が、微細化の鈍化による不振を補い始めている。例えば、AMDやNVIDIAは、GPUとメモリを並列に並べ、シリコンインターポーザーで接続するという2.5D(2.5次元)のハイエンドグラフィックスプロセッサを発表した。

GLOBALFOUNDRIESの最高技術責任者(CTO)であるGary Patton氏によると、シリコントランジスタの小型化が進んできた一方でパッケージの小型化はそこまで進んでいないという。GLOBALFOUNDRIESは、Micron Technologyの「HMC(Hybrid Memory Cube)」とロジックチップをTSV(シリコン貫通ビア)で接続したデバイスを、約2年にわたり製造してきた。

Qualcommは2016年初め、スマートフォン向けSoC用のTSV技術が、近い将来に発展するとは見ていないことを明らかにした。熱を分散するのが難しい上に、コストが掛かるプロセスであるからだ。一方、QualcommのRoawen Chen氏は、他の可能性を見いだしている。

Chen氏は「パッケージはダイのように大幅に小型化していないので、その中にはどう使っていいのか分からないスペースがある。メモリは、そのスペースを用いるためだけに統合されるだろう」と述べた。

その上で、QualcommがTSMCの「InFO(Integrated Fan Out)」などのパッケージング技術に関心を寄せていることに言及した。InFOは、「iPhone」向け10nmプロセスSoCに使われるパッケージング技術として、Appleが採用するのではないかとうわさされている。

IMECのCEOであるLuc Van den Hove氏は、「長期的には、ロジックメーカーは、現在NAND型フラッシュメモリメーカーが用いているようなモノリシックな3D(3次元)技術を導入するのではないか」とみている。同氏は、IMECがReRAM(抵抗変化型メモリ)で開発したような積層トランジスタを、SRAMやFPGAなど標準的なロジックブロックに用いることで、超高密度のチップを生み出すことができると述べた。

この他IMECは、2.5Dデバイス向けに超高速のチャンネルを作るべく、シリコンフォトニクスの開発にも力を入れている。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

IMECは、より高密度な2.5Dのチップの開発を進めるべく、オンチップのオプティカルリンクを研究している 出典:IMEC

IMECは、より高密度な2.5Dのチップの開発を進めるべく、オンチップのオプティカルリンクを研究している 出典:IMEC