「SEMICON West 2016」、7nm世代以降のリソグラフィ技術(Applied Materials編):福田昭のデバイス通信(92)(2/2 ページ)

コンタクト金属は7nmでタングステンからコバルトへ

7nm世代のFinFETは、フィンをさらに高く、さらに狭くし、フィンのピッチをさらに詰めることになる。フィンのアスペクト比(縦横比)はさらに大きくなり、薄膜形成には原子層単位の成膜技術を駆使する。

寄生容量を削減するため、絶縁膜の比誘電率はさらに下げることが求められる。エアギャップ絶縁の導入を考慮するようになるだろう。

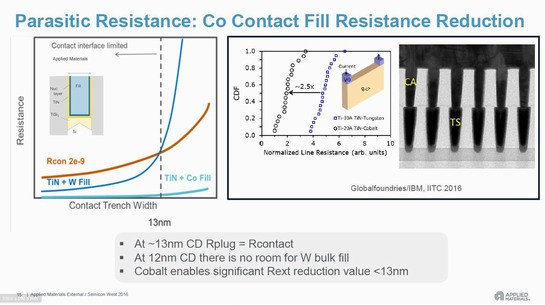

コンタクトはそのまま微細化すると抵抗値が大きく上昇してしまう。従来のコンタクト用金属材料であるタングステン(W)に換わり、コバルト(Co)を使うことで抵抗増大を抑えるようになる。

コンタクト抵抗の増加と抑制。コンタクトを埋める金属をタングステン(W)からコバルト(Co)に変更することで、コンタクト抵抗の増加を抑える。Applied Materialsの講演スライドから(クリックで拡大)

コンタクト抵抗の増加と抑制。コンタクトを埋める金属をタングステン(W)からコバルト(Co)に変更することで、コンタクト抵抗の増加を抑える。Applied Materialsの講演スライドから(クリックで拡大)5nm世代はフィン(Fin)からゲートオールアラウンド(GAA)へ

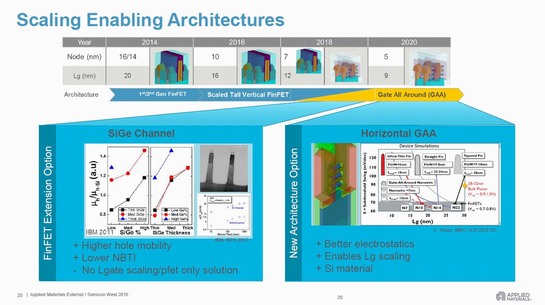

次の5nm世代になると、FinFETの限界が見えてくる。微細化の原則に従うと、フィンをさらに高くし、フィンのピッチをさらに詰めることになる。ところがフィンがあまりに薄くなってしまい、フィンの厚みのばらつきを抑えられない。従ってトランジスタのしきい値電圧のばらつきが増加してしまう。

そこで2つの選択肢が考えられている。1つは、チャンネルの材料をシリコン(Si)から、シリコンゲルマニウム(SiGe)に変更することである。キャリアには伝導電子(エレクトロン)と正孔(ホール)があるが、SiGeチャンネルだとホールの移動度が上がる。ただしこのソリューションだと、pチャンネルFinFETの性能しか上昇しない。実効的にはnチャンネルFinFETが微細化されないのが難点である。

もう1つの選択肢は、トランジスタの構造を変更することだ。チャンネルを複数の微細な円柱形状(「Siナノワイヤ」と呼ぶ)に変更し、周囲をゲート電極で囲む。この構造は、「GAA(Gate All Around)」と呼ばれている。GAAではゲートによる制御性が大幅に向上するとともに、短チャンネル効果を抑制できる。

(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

「SEMICON West 2016」、7nm世代以降のリソグラフィ技術(imec編)

「SEMICON West 2016」、7nm世代以降のリソグラフィ技術(imec編)

imecは次世代のリソグラフィ技術を展望するフォーラムの講演で、半導体デバイスの微細化ロードマップを披露した。このロードマップでは、微細化の方向が3つに整理されている。シリコンデバイスの微細化、シリコン以外の材料の採用、CMOSではないデバイスの採用だ。imecは、CMOSロジックを微細化していく時の課題についても解説した。 ARMから見た7nm CMOS時代のCPU設計(14)〜次々世代の異次元トランジスタ

ARMから見た7nm CMOS時代のCPU設計(14)〜次々世代の異次元トランジスタ

今回は、トランジスタ密度をFinFETに比べて、より高められる素子の構造について触れる。代表的なものが、円筒状のチャンネルをウエハー表面と平行に配置する「ホリゾンタルナノワイヤ(HNW)」と、垂直に配置する「バーチカルナノワイヤ(VNW)」である。 FinFETの次なるトランジスタはナノワイヤ?

FinFETの次なるトランジスタはナノワイヤ?

ベルギーで開催された「IMEC Technology Forum 2016(ITF 2016)」(2016年5月24〜25日)では、FinFETの次なるトランジスタとして、ナノワイヤが話題に上った。 「SEMICON West 2016」、半導体露光技術の進化を振り返る(前編)

「SEMICON West 2016」、半導体露光技術の進化を振り返る(前編)

今回から、リソグラフィ技術のセッションの概要を紹介する。まずは、半導体露光技術の進化について解説したい。前半では主に、「コンタクト露光」から始まる等倍露光技術の発展の流れを見てみよう。 微細化、「3nmまでいくのでは」

微細化、「3nmまでいくのでは」

「ムーアの法則」の生みの親であるGordon Moore氏が、ハワイの自宅でベルギーIMECのビデオインタビューに応じ、未来の技術に関する自身の見解や、1965年以来半導体業界に大きな影響を及ぼし続けてきたムーアの法則の今後について語った。87歳となった同氏は、謙虚なエンジニアはいつまでも自分を笑いの種として語れることを示してみせた。 ARMの新ベクトル命令「SVE」、ポスト京に採用へ

ARMの新ベクトル命令「SVE」、ポスト京に採用へ

米国で開催された「Hot Chips 28」において、ARMが新しいベクトル命令「SVE(Scalable Vector Extensions)」を発表した。富士通が、2020年を目標に開発しているポスト「京」スーパーコンピュータに採用されることが決まっている。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増