「SEMICON West 2016」、7nm世代以降のリソグラフィ技術(Applied Materials編):福田昭のデバイス通信(92)(1/2 ページ)

Applied Materialsの講演では、MOSFETの微細化ロードマップと、微細化の手法および課題が解説された。7nm世代のFinFETでは、フィンを狭く、高くするとともにコンタクト用の金属材料を変える必要が出てくる。FinFETの限界が見え始める5nm世代では、微細化の手法として主に2つの選択肢がある。

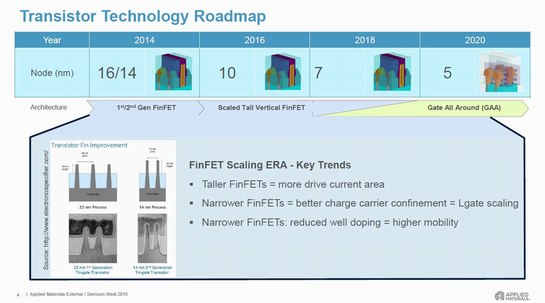

ロジック用トランジスタの微細化ロードマップ

半導体製造装置と半導体製造用材料に関する北米最大の展示会「SEMICON West 2016」が7月12日〜14日に米国カリフォルニア州サンフランシスコのモスコーンセンター(Moscone Center)で開催された。12日には「FORUM」(フォーラム)と称する併設の講演会があり、専門テーマに関する解説や展望などを数多くの研究者や技術者、経営者などが発表した。

中でも興味深かったのは、次世代のリソグラフィ技術を展望するフォーラムである。午前中には「Lithography: Charting a Path, or Paths, Between Nodes 10 and 5」と題するフォーラムが、午後には「Node 10 to node 5 - Dealing with the Slower Pace of Traditional Scaling」と題するフォーラムが開催された。本コラムではまず、午前のフォーラムから主だった講演の概要をご報告した。前々回からは、午後のフォーラムから主な講演の概要をご紹介している。

今回は、半導体製造装置大手のApplied MaterialsでTechnical Projects, Transistor and Interconnect Groupのシニアディレクターを務めるMichael Chuzik氏の講演概要をご報告する。講演タイトルは「Fins and Wires, How Do We Get To 5nm ?」である。講演では、CMOSロジックを支えるMOSFET(トランジスタ)の微細化ロードマップを示し、微細化の手法と課題を説明していった。

現行の最新世代である16/14nm世代のロジック用トランジスタにはFinFET(フィンFET)が使われている。シリコンのチャンネルをフィン状にすることで、微細化を可能にしたトランジスタ技術である。

10nm世代では、FinFETのフィンを狭く、高くすることで微細化を実現することが確実になっている。フィンを狭くしてフィンのピッチを詰めることで、基本寸法を短くする。同時にウエルのドーピング濃度が下がり、キャリアの移動度が上がる。フィンの高さを上げることは、トランジスタの電流駆動能力を向上させる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増