ARMの新ベクトル命令「SVE」、ポスト京に採用へ:スパコン市場でx86を追う

米国で開催された「Hot Chips 28」において、ARMが新しいベクトル命令「SVE(Scalable Vector Extensions)」を発表した。富士通が、2020年を目標に開発しているポスト「京」スーパーコンピュータに採用されることが決まっている。

ポスト「京」に向けたARMの拡張命令

ARMは、同社の64ビットアーキテクチャ「ARMv8」をHPC(高性能コンピューティング)向けに推進していくためのベクトル命令を開発した。富士通は、この拡張命令の開発をサポートしており、理化学研究所(理研)と共同開発したスーパーコンピュータ「京(けい)」の後継機に採用する考えだという。京は、SPARCベースのシステムで、2011年のスーパーコンピュータ処理能力ランキング「TOP500」において、8PFLOPS(ペタフロップス)を達成し、世界第1位の座を獲得している。

スーパーコンピュータ市場ではこれまで、Intelのx86が優勢を維持してきたため、ARMの存在感が希薄だった。だが、今回の取り組みにより、ARMのプロセッサコアを初めて同市場に参入させていくことになる。ARMは、Intelのように同市場での存在感を高めていくことにより、IBMやCrayなどのプロセッサを徐々に置き換えていきたい考えだ。

ARMの強みは、x86よりも高い電力効率を実現できる可能性を秘めているという点にある。現在、スーパーコンピュータの開発メーカーにとって、エクサ(1エクサは10の18乗、100京に相当する)FLOPS級のシステムを構築し、それを駆動するための大量の電力を供給することは非常に難しいが、ARMはその実現をサポートできる可能性を持っている。

ARMが「SVE」を発表

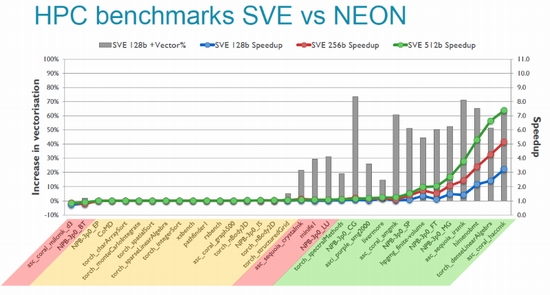

ARMが現在サポートしている「Neon SIMD」命令は、128ビットに制限されており、クライアントシステムのイメージングやビデオでの使用に焦点を当てている。しかし、同社の「SVE(Scalable Vector Extensions)」は、128〜2048ビット長を128ビット単位でサポートするという。ベクトルコードを1回書き込めば、あらゆるサイズのベクトル設計で動作させることができ、再コンパイルも不要だ。ARMは、「他のアーキテクチャでは実現不可能な性能だ」と主張する。

富士通は、「2020年までには京の後継機でSVEを利用し、既存システムの50倍の高性能化と15倍の高効率化を実現したい」と述べる。

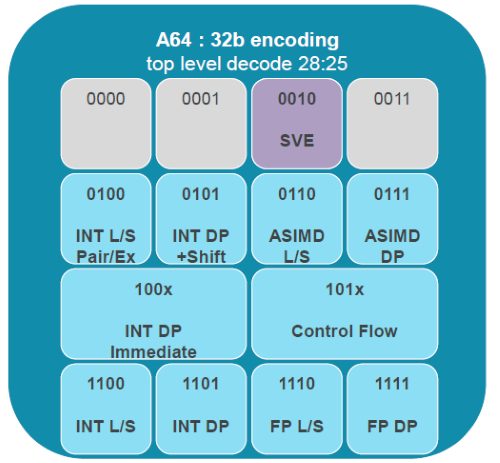

ロードストアアーキテクチャであるSVEは、最大32のベクトルレジスタと16のプレディケートレジスタの他、制御レジスタやファーストフォルトレジスタなどを使用する。プレディケートレジスタは、制御ループに関するさまざまな判断を管理するために使われる。ARMは、将来的にSVEを拡張するためのスペースを、プログラミング領域内に確保しているという。

SVEは現在、数多くのパートナー企業との協業によって開発が進められており、2017年初めには一般に提供できるようになる見込みだ。ARMは現在、拡張命令に向けたオープンソースのLinuxパッチを作成するための手法の開発に着手したところだという。

ARMのフェローであり、リードアーキテクトを務めるNigel Stephens氏は、半導体チップのカンファレンスである「HOT CHIPS 28」(米カリフォルニア州クパチーノ、2016年8月21〜23日)において講演を行った後、「ARMの64ビットのライセンス供与先企業は全て、SVE技術を使用することができる。当社は現在、複数のパートナー企業との協業によりSVEの開発を進めているが、これらの企業名について公表するつもりはない」と述べている。

富士通にとって今回の協業は、ARMが高性能システム市場に参入するに当たり、パートナー契約を締結するチャンスだったといえる。

SPARCは、富士通の法人向けサーバでは、より好んで採用されている。だが同社は、ARMチップをベースにした新しいシステムにも機会を見いだしているという。富士通は2020年までにエクサFLOPS級のスーパーコンピュータの実現を目指している。同社アドバンストシステム開発本部 プロセッサ開発統括部 第一開発部 部長 吉田利雄氏によれば、富士通は512ビットのSIMDベクトルユニットと「Tofuインターコネクト」を使用する予定だという。

【翻訳:田中留美、編集:EE Times Japan】

関連記事

ソフトバンク史上最大の賭けに出た孫氏の思惑

ソフトバンク史上最大の賭けに出た孫氏の思惑

なぜ、ソフトバンクはARMを買収したのか? 狙いはどこにあるのか? いろいろな見方が広がっている中で、いま一度、ソフトバンクが行ってきた大きな投資を振り返りながら、ARM買収の意味を考えた。 ARM、TSMCと7nm FinFET開発で協業

ARM、TSMCと7nm FinFET開発で協業

ARMとTSMCが、データセンサーやネットワークインフラ向けに、7nm FinFET開発で協業する。サーバ市場での勢力拡大に積極的なARMは、7nmプロセスの採用によるチップの高性能化を非常に重要視していると専門家は話す。 求む、「スーパーメモリ」

求む、「スーパーメモリ」

ARM Researchの講演内容を紹介してきたシリーズ。完結編となる今回は、ARMが「スーパーメモリ」と呼ぶ“理想的なメモリ”の仕様を紹介したい。現時点で、このスーパーメモリに最も近いメモリは、どれなのだろうか。 省電力で二冠を達成したスパコン「TSUBAME」、鍵は“油に浸して冷却する”

省電力で二冠を達成したスパコン「TSUBAME」、鍵は“油に浸して冷却する”

省エネ性能ランキングで世界一となった、東京工業大学のスーパーコンピュータ「TSUBAME-KFC」。消費電力の低減の鍵となったのは、油浸冷却システムの採用である。 IBMのスパコン、ガン治療費の削減に光明

IBMのスパコン、ガン治療費の削減に光明

陽子線をガン細胞に照射して死滅させる陽子線治療。ガンの最先端治療として期待されているが、費用が高額で、照射ポイントの決定に時間がかかるのがデメリットとなっている。IBMの基礎研究所は、スーパーコンピュータを利用することで、陽子線治療の費用を下げられると提案する。 なぜ「京」がスパコン1位を獲得できたのか

なぜ「京」がスパコン1位を獲得できたのか

SPARCプロセッサを採用したことだけが勝因ではない。インターコネクト性能とプロセッサ性能のバランスが良いことが理由だ。TOP500で最も消費電力が大きなスーパーコンピュータでもあるが、エネルギー効率は4位と優れている。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 「装置は動くがプロセスが成立しない」――He供給危機とナフサ不足の本質

- He/ナフサ供給危機で工場新設も遅延? 装置/チップメーカーへの波及経路を探る

- 最新ノートPC5機種を分解 新旧MacBook Proの中身の違いは?

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 「AI特需」の恩恵届かぬ日本企業 Gartnerが見る2026年半導体市場

- 「Rapidusの隣」に光電融合パッケージ開発拠点、28年度の完成目指す

- Apple新CEOはエンジニア出身 製品開発重視への回帰か

- ローム・東芝・三菱電機のパワー半導体はどうなるか

- シリコンフォトニクスと先進パッケージの統合が描く未来

SVEは、64ビットのARMコア上でのみ使用できるという

SVEは、64ビットのARMコア上でのみ使用できるという