「SEMICON West 2016」、imecが展望する5nm世代の配線技術(前編):福田昭のデバイス通信(94)(2/2 ページ)

微細化によって配線抵抗とRC積が急激に増加

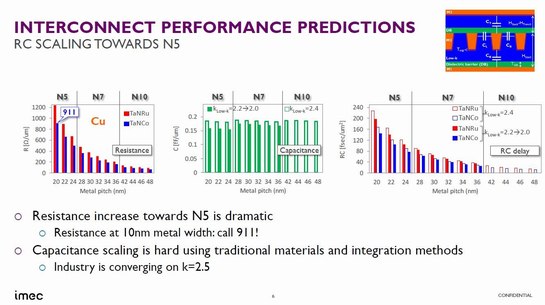

10nm世代から7nm世代、5nm世代の配線パラメータと、配線による遅延時間を展望すると、厳しい将来が浮かび上がって来る。なお配線ピッチを10nm世代では48nm〜42nm、7nm世代では36nm〜28nm、5nm世代では24nm〜20nmと仮定した。

まず配線抵抗(R)である。配線長(μm)当たりの抵抗値は配線ピッチの短縮とともに急速に上昇していく。エレクトロマイグレーションの問題が厳しくなる銅(Cu)に換わり、金属配線はコバルト(Co)またはルテニウム(Ru)を主材料とするようになる。

10nm世代ではμm当たりの抵抗値は100Ω未満でそれほど高くはない。ところが7nm世代では200Ω〜400Ωに上昇する。そして5nm世代では900Ω〜1200Ωという、金属配線なのに抵抗素子のような値にまで、高くなってしまう。

続いて配線容量(C)である。容量(C)は、配線長(μm)当たりで1.5fF〜2.0fFを維持していくことが求められる。いやむしろ、世代ごとに下げていくことが望ましい(配線抵抗が上昇するので)。すると層間絶縁膜の比誘電率は、2.4が最大水準となり、微細化とともに2.2、さらには2.0へと下げることが求められる。

そしてRC積(遅延時間)は、微細化とともに抵抗(R)が増大するので、当然ながら伸びていく。10nm世代では、単位面積(平方μm)当たりのRC積(遅延時間)は20fs(フェムト秒)前後と非常に短い。ところが7nm世代では、配線ピッチが狭まるとともに40fsから100fs(0.1ps)と急激に増加していく。5nm世代では、単位面積(平方μm)当たりのRC積は200fsに達する。ただし、層間絶縁膜の比誘電率を2.0に下げることでRC積を140fsにまで下げられる。

これらの事実は、従来の配線技術(銅(Cu)の配線材料と比誘電率2.5の層間絶縁材料)では微細化に対応できないことを示している。新しい技術の導入によって配線抵抗(R)と配線容量(C)を最適化しなければならない。

(後編に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

「SEMICON West 2016」、Synopsysが予測する5nm世代のトランジスタ技術

「SEMICON West 2016」、Synopsysが予測する5nm世代のトランジスタ技術

Synopsysの講演では、5nm世代のトランジスタのシミュレーション評価結果が報告された。この結果からはFinFETの限界が明確に見えてくる。5nm世代に限らず、プロセスの微細化が進むと特に深刻になってくるのが、トランジスタ性能のばらつきだ。 “他にないスライス技術”がSiCの生産効率を4倍へ

“他にないスライス技術”がSiCの生産効率を4倍へ

半導体製造装置メーカーであるディスコは、今までにない手法を用いたレーザー加工によるインゴットスライス手法「KABRA(カブラ)」プロセスを開発したと発表した。SiC(炭化ケイ素)ウエハー生産の高速化、取り枚数増を実現し、従来方式と比較して生産性を4倍向上させることが可能という。 ゲート長1nmのトランジスタ、CNT活用で米が開発

ゲート長1nmのトランジスタ、CNT活用で米が開発

米国のローレンスバークレー国立研究所が、カーボンナノチューブ(CNT)をゲートに用いて、ゲート長がわずか1nmのトランジスタを開発した。 Intel、「ムーアの法則は微細化の実現ではない」

Intel、「ムーアの法則は微細化の実現ではない」

「ISPD 2016」においてIntelは、10nmプロセス以降もCMOSに注力する考えであることを明らかにした。同社はそこで、ムーアの法則は微細化そのものというわけではなく、より多くのダイをウエハー上に形成することで利益を確保することだと、述べている。 スピン注入型MRAMの不都合な真実

スピン注入型MRAMの不都合な真実

STT-MRAMの基礎を解説するシリーズ。最終回となる今回は、磁気トンネル接合(MTJ)を構成する固定層や磁性層に焦点を当てる。スピン注入型MRAMのMTJは、47層もの層で構成されている。これほどの層が必要なのにはきちんとした理由があるのだが、実は同時にそれがSTT-MRAMの弱点にもなっている。 Intelモバイル撤退の真相――“ARMに敗北”よりも“異端児SoFIA”に原因か

Intelモバイル撤退の真相――“ARMに敗北”よりも“異端児SoFIA”に原因か

今回は、2016年5月に明らかになったIntelのモバイル事業からの撤退の真相を、プロセッサ「Atom」の歴史を振り返りつつ探っていく。「Intelは、ARMやQualcommに敗れた」との見方が強いが、チップをよく観察すると、もう1つの撤退理由が浮かび上がってきた。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増