「SEMICON West 2016」、imecが展望する5nm世代の配線技術(後編):福田昭のデバイス通信(95)(2/2 ページ)

多孔質絶縁材料をエッチング用プラズマから守る

続いて配線容量(C)の最適化である。最適化といっても、層間絶縁膜の比誘電率を最小化することで、配線容量をなるべく低くすることに相当する。

現在は材料レベルでの誘電率低減は限界に達しつつある。最も誘電率の低い材料は大気あるいは真空(比誘電率は1.0)なので、数多くの孔を内蔵する多孔質の誘電体材料(Porous Materials)が、究極の低誘電率材料として選ばれている。比誘電率が2.4以下の層間絶縁膜材料は、多孔質材料でなければほぼ、実現できない。

ただし、多孔質材料はいくつもの問題点を抱える。その代表が、プラズマエッチングによって大きな損傷(厳密には材料組成が変化して比誘電率が上昇する)を受けることだ。このため、プラズマによる損傷を緩和したり、あるいは、損傷を修復したりといった技術が必要となる。

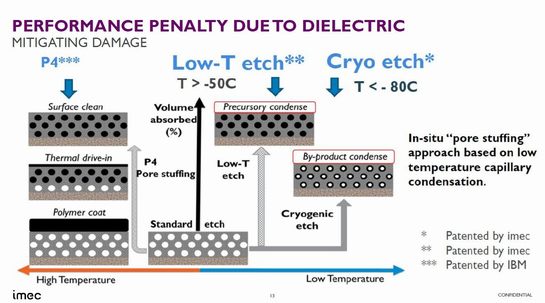

多孔質の低誘電率絶縁材料をプラズマから保護する技術の代表は、IBMが開発したP4(Post Porosity Plasma Protection)技術と、imecが開発したクライオエッチ(クライオジェニックエッチング、Cryogenic Etching)技術である。P4技術では、高温で分解する高分子材料によって孔(Pore)を充てんする。プラズマエッチングなどの一連のプロセスが完了した後で、高温処理によって充てん材料を分解する。

クライオエッチ技術では、プラズマの温度をマイナス80℃以下の低温に下げ、エッチング用ガス分子が低温下で凝縮した膜によって孔の内壁を薄く覆うことで、ダメージを軽減する。

3次元化によって配線長を短くする

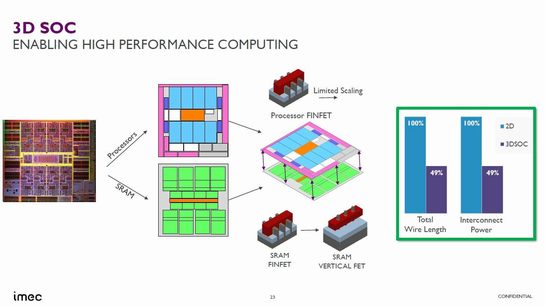

講演者のWilson氏はさらに、配線長を短縮するために3次元積層した高性能プロセッサというアイデアを示した。高性能のマルチコアプロセッサでは大容量のSRAMキャッシュを搭載する。シリコンダイ面積は大きくなり、従って配線が長く、配線抵抗が高く、配線容量が大きくなってしまう。

そこでプロセッサ全体をSRAMキャッシュ層とCPUコア層に分割し、2層構造とする。この結果、トータルの配線長が半分に短くなるとともに、配線による消費電力も半分に減少する。

そしてCPUコア層はトランジスタをFinFETのままにしておき、微細化のペースを緩やかにする。一方でSRAMキャッシュ層はトランジスタをナノワイヤFETにすることで微細化を進め、キャッシュの容量を拡大する。シリコンダイ面積を変えずにキャッシュ容量を拡大することで、プロセッサの処理性能を高める。

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

Samsung、10nm SoCの量産を2016年内にも開始か

Samsung、10nm SoCの量産を2016年内にも開始か

Samsung Electronics(サムスン電子)が10nm FinFETプロセスを適用したSoC(System on Chip)の量産体制を着々と整えているようだ。「Galaxy Note 7」の発火問題で同社のファンドリー事業も停滞するとみられているが、最先端プロセスの実用化に向け、開発を進めている。 「SEMICON West 2016」、Synopsysが予測する5nm世代のトランジスタ技術

「SEMICON West 2016」、Synopsysが予測する5nm世代のトランジスタ技術

Synopsysの講演では、5nm世代のトランジスタのシミュレーション評価結果が報告された。この結果からはFinFETの限界が明確に見えてくる。5nm世代に限らず、プロセスの微細化が進むと特に深刻になってくるのが、トランジスタ性能のばらつきだ。 ソニー製チップの採用でFD-SOIへの関心高まる?

ソニー製チップの採用でFD-SOIへの関心高まる?

28nm FD-SOIプロセスを採用したソニーのGPSチップが、中国のスマートウォッチに搭載された。FD-SOIプロセスに対する関心が高まる可能性がある。 半導体プロセス技術、開発競争が過熱

半導体プロセス技術、開発競争が過熱

FinFETの微細化が進む一方で、FD-SOI(完全空乏型シリコン・オン・インシュレーター)にも注目が集まっている。専門家によれば、2025年までは28nm FinFETプロセスが優勢だとするが、それ以降はFD-SOIが伸びる可能性もある。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ロームとデンソー、東芝、三菱電機……国内パワー半導体再編の行方

- AIの競争軸は半導体から電力へ――日本の戦略の「死角」に

- IntelとSambaNova、提携の行く末――「最もあり得るシナリオ」は?

- ローム、デンソーによる買収提案は「事実」

- 目指すは500nm RDL 太陽HDがimecと挑む次世代パッケージング材料

- 「NVIDIAとGroqの取引」がAI新興にもたらした2つの効果

- ダイヤモンドMOSFETで初の200V、1AのSW動作を達成

- 25年Q4の半導体企業ランキング、キオクシアが13位に上昇

- ロームと東芝、半導体事業の提携強化へ「協議を継続中」

- 「世界最高」品質の量子光、誤り耐性型量子コンピュータに貢献