ムーアの法則の“新たな意味”とは:3DやInFOで微細化を補う(2/2 ページ)

「シリコン4.0」を開くInFO技術

またLu氏は、「現在の半導体業界は、垂直トランジスタに移行しつつある“シリコン2.0”時代にある。今後は、ますます多くの半導体メーカーが3次元構造を採用する“シリコン3.0”時代へと突入していくだろう」と述べている。

Lu氏は論文の中で、“シリコン4.0”以降の半導体業界についての見解を示している。同氏は、「シリコン4.0に前進することで、AR(拡張現実)やVR(仮想現実)、AI(人工知能)など数多くの新たなアプリケーションが実現できる」と述べている。「次の変換点となるのは、ヘテロジニアスインテグレーション(異種統合)だ。具体的には、TSMCが開発したパッケージング技術である『InFO(Integrated Fan Out)』のような技術を使ったシリコンとノンシリコン材料が、シリコン4.0への扉を開く」と同氏は言う。

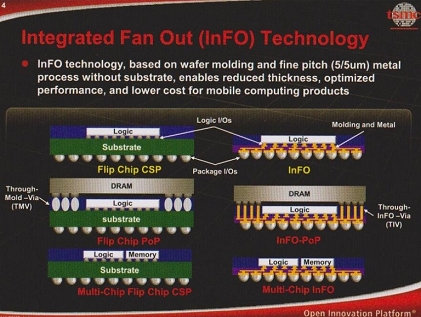

InFOは、半導体のエッジ部分にボンディングパッドを配置するパッケージング技術だ。同技術によって配線基板が不要になり、パッケージを20%薄くし、処理速度を20%、熱性能を10%改善することができるという。

Infineon Technologies(インフィニオン・テクノロジーズ)は2008年に、低コスト化とパッケージの低背化を図るために「eWLB(embedded Wafer-Level Ball grid array)」として同技術を開発した。だが、TSMCがInFOを実用化するまでは、歩留まりの問題がこの新たな技術の導入を妨げていた。

Lu氏は、「InFO技術は、シリコン4.0の幕開けとなるだろう」と述べる。同氏は、「もう1つの革新技術は、『TIV(Through-InFO-Via)』だ。TIVは、ダイを外部に接続するための柱のようなものだ。InFOとTIVによって、シリコンの外側から水平/垂直の両方向の接続が可能になる。これがヘテロジニアスインテグレーション技術を持続する鍵となる。以前はInFO技術がなかったため、TIVを有効に活用できなかった」と続けた。

「InFO技術によって、半導体をレンズやセンサー、アクチュエーターなどの部品と直接接続できるようになる。これらの部品はシステムに搭載されているが、まだ十分に小型化されていない」とLu氏は指摘する。「これが、InFO技術を活用したシリコンとノンシリコンのヘテロジニアスインテグレーションだ。現在、これらの部品は全て、PCB(プリント基板)に集積されていて消費電力が大きい。光学素子の消費電力と比べると5桁も違う」と述べている。

Lu氏は、「シリコン4.0に向けて、ファウンドリーや半導体設計企業、システムハウスが協力することで新たな可能性が生まれる」と予想している。同氏は、「半導体は3000億米ドルの産業だ。だが、家電産業は1兆6000億米ドル規模の市場を形成している」と指摘する。

Lu氏は、「システムメーカーは、小型で低消費電力のデバイスを開発するために、ヘテロジニアスインテグレーションが必要になる」と述べている。

同氏は、「ムーアの法則が物理的に収束を迎えるまでに、あと2世代ある。そのため、3次元ゲートや3D NANDフラッシュ、InFOなどは問題なく導入されるだろう。トランジスタは5nmまで微細化され、それは実質的には1nmプロセスを適用した時の性能と同等レベルになるだろう」と予想している。

【翻訳:滝本麻貴、田中留美、編集:EE Times Japan】

関連記事

中身が大変身した「iPhone 7」とその背景

中身が大変身した「iPhone 7」とその背景

2016年9月に発売されたAppleの新型スマートフォン「iPhone 7」。一部では、あまり目新しい新機能が搭載されておらず「新鮮味に欠ける」との評価を受けているが、分解して中身をみると、これまでのiPhoneから“大変身”を果たしているのだ。今回は、これまでのiPhoneとiPhone 7の中身を比較しつつ、どうして“大変身”が成されたのかを考察していこう。 微細化、「3nmまでいくのでは」

微細化、「3nmまでいくのでは」

「ムーアの法則」の生みの親であるGordon Moore氏が、ハワイの自宅でベルギーIMECのビデオインタビューに応じ、未来の技術に関する自身の見解や、1965年以来半導体業界に大きな影響を及ぼし続けてきたムーアの法則の今後について語った。87歳となった同氏は、謙虚なエンジニアはいつまでも自分を笑いの種として語れることを示してみせた。 半導体業界、“細分化”から“統合”へ

半導体業界、“細分化”から“統合”へ

半導体業界の歴史において、2015年ほど大規模な企業統合が繰り返された年はなかっただろう。ムーアの法則を維持すべく新しい技術を生み出してきた半導体業界では、どちらかといえば、企業は“細分化”する傾向にあったからだ。 TSMC、Apple「A10/A11」をほぼ独占的に製造か

TSMC、Apple「A10/A11」をほぼ独占的に製造か

TSMCは、Appleの「iPhone」向けプロセッサ「A10」および「A11」(仮称)の製造を、ほぼ独占的に製造することになるとみられている。もう1つのサプライヤーであるSamsung Electronics(サムスン電子)に対する優位性をもたらしたのは、独自のパッケージング技術「InFO」だという。 ASML、次世代EUV装置に19億米ドルを投資

ASML、次世代EUV装置に19億米ドルを投資

半導体製造装置メーカーのASMLは、2017年出荷予定の第1世代EUV(極端紫外線)リソグラフィ装置の後継となる次世代EUV装置の開発計画を明らかにした。2024年ごろの量産を目指し、約19億米ドルの投資を行うという。 GFの7nm FinFETプロセス、2018年にも製造開始へ

GFの7nm FinFETプロセス、2018年にも製造開始へ

GLOBALFOUNDRIES(GF)が、7nm FinFETプロセスの開発計画を発表した。2018年後半には同プロセスでの製造を開始する予定だという。さらに、同じく2018年には、22nm FD-SOI(完全空乏型シリコン・オン・インシュレーター)プロセスで製造するチップにおいて、ギガビット未満の低容量の混載MRAM(磁気抵抗メモリ)をサポートする予定だ。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- パワー半導体再編が本格化 ローム・東芝・三菱電機が協議開始へ

- 「究極の半導体」ダイヤモンドを社会へ 動態展示も実現の早大発新興

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- 「Renesas 365」がついに始動 「不可能だった規模」の検証、数分で

- JDIが鳥取工場を売却、車載用液晶パネル拠点

- もはや半導体メーカーの域を超えた NVIDIA最新エッジ機器を分解

- 魚津はTower、砺波はNuvotonに TPSCo事業の再編を発表

- ソニー、新会社「BRAVIA」にテレビ事業を承継 企業価値1028億円

- シャープ新社長は海外事業出身 鴻海と連携で「新たな成長ステージへ」

TSMCの「InFO」パッケージング技術 出典:TSMC

TSMCの「InFO」パッケージング技術 出典:TSMC