NVIDIAがエネルギー効率の高い相互接続チップを試作:福田昭のデバイス通信(101) 高性能コンピューティングの相互接続技術(6)(1/2 ページ)

相互接続(インターコネクト)のエネルギー効率を高める技術の1つである「バランス型電荷再利用バス(BCRB:Balanced Charge Recycling Bus)」。今回は、BCRB技術のバスを搭載したテストチップの概要と、実験結果について解説する。

バランス型電荷再利用バスのテストチップを製造

2016年12月に開催された国際学会IEDMのショートコースから、「将来のコンピュータにおける相互接続の課題(Interconnect Challenges for Future Computing)」と題するNVIDIAの講演概要をご紹介している。講演者はNVIDIAで研究担当シニア・バイスプレジデント兼チーフサイエンティストを務めるWilliam(Bill) Dally氏である。

シリーズの第5回である前回は、エネルギー効率の高い相互接続技術である、バランス型電荷再利用バス(BCRB:Balanced Charge Recycling Bus)技術を説明した。今回は、BCRB技術のバスを載せたテストチップの概要と、実験結果を解説する。

なお講演だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、Dally氏の講演内容を適宜、補足している。あらかじめご了承されたい。

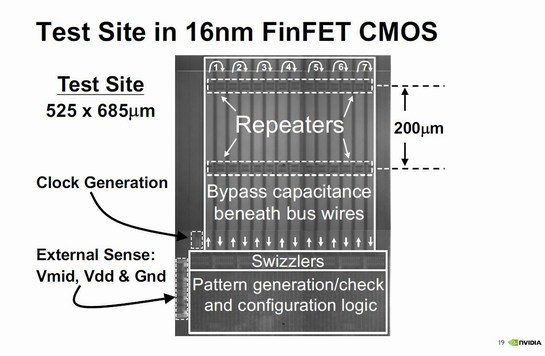

前回に説明したBCRB技術とContraflow Wiring(隣接する平行な伝送路で信号の方向を逆向きにする)技術の効果を実際に検証するため、テストチップを試作した。製造技術は16nm CMOSのFinFETである。シリコンダイの寸法は525μm×685μm。

伝送路の長さは全長6mmと全長8mmの2種類がある。伝送路は200μmごとにリピータ(CMOSインバータ)を配置した。伝送路の一端はロジック回路、反対側の一端は折り返しとなっている。ロジック回路には伝送路をツイストさせる回路(Swizzler)と信号パターン発生回路、信号パターン検査回路などを載せた。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- キオクシア25年度 驚異の決算 Q4純利益は前年比30倍

- JDI、25年度Q4は4年ぶり黒字 上場廃止は「必ず阻止」

- iPhone好調で過去最高も、「世界一」維持へ動くソニー半導体

- 「膿み出し切った」SiC関連減損で過去最大1584億円赤字 ローム

- パワー半導体3社連合とデンソー提携のアナログ「両軸を強化」 ローム社長

- 加賀電子が新光商事にTOB、完全子会社化へ

- 「技術ナンバーワンであり続ける」 ソニーセミコンCTOが語る技術戦略

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- AIの「トンデモ判断」で本番DBが全飛び! 他山の石にしたいAIコーディングの落とし穴