2.5D(2.5次元)の新世代パッケージング技術:福田昭のデバイス通信(104) TSMCが解説する最先端パッケージング技術(3)(1/2 ページ)

TSMCが開発した2.5次元のパッケージング技術「CoWoS(Chip on Wafer on Substrate)」と「InFO(Integrated Fan-Out wafer level packaging)」を解説する。CoWoSでは、「シリコンインターポーザ」の導入により、樹脂基板では困難な微細配線が可能になった。InFOは、樹脂基板とバンプを省いたことで、低コストで高密度な再配線構造を形成できるようになり、パッケージの小型化と薄型化を実現した。

シリコンによる中間基板(インターポーザ)の導入

2016年12月に開催された国際学会IEDMのショートコース講演(技術解説講演)から、「システム集積化に向けた最先端パッケージング技術(Advanced Packaging Technologies for System Integration)」と題する講演の概要をシリーズでご紹介している。講演者はシリコンファウンドリー最大手のTSMCでシニアディレクターを務めるDouglas Yu氏である。なお講演内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、Yu氏の講演内容を筆者が適宜、補足している。あらかじめご了承されたい。

前回は、複数のチップ(シリコンダイ)を1個のパッケージにまとめる理由を説明するとともに、シリコン貫通ビア(TSV:Through Silicon Via)技術によってシリコンダイを積層する3D IC(Three-dimentional Integrated Circuit)は、技術的な難しさや製造コストの上昇などの問題を抱えていることを指摘した。

そこで登場したのが、2.5D(2.5次元)あるいは2.nD(2.n次元)などと呼ばれる、新世代のパッケージング技術である。TSMCは、「CoWoS(Chip on Wafer on Substrate)」と呼ぶ2.5次元のパッケージング技術を開発し、主に高性能コンピューティング分野で製品化してきた。

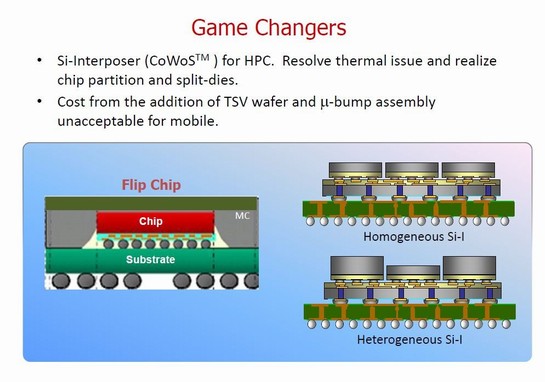

CoWoS技術の最大の特徴は、「シリコンインターポーザ(Silicon Interposer)」と呼ぶ中間的な基板の導入にある。パッケージ基板(樹脂基板)の上にシリコンの中間基板(インターポーザ)を置き、その上に複数のシリコンダイを横に近接して並べる。シリコンインターポーザの表面(上側)には、多層配線の回路を形成してあり、TSVによって裏面(下側)の樹脂基板と接続する。

ここで重要なのは、シリコンインターポーザにはトランジスタやダイオードといった能動素子が形成されていないことだ。単なる再配線基板であり、載せるのは受動素子にとどまる。このため、樹脂基板では困難な微細配線をシリコンで形成可能にするとともに、ロジックやメモリなどの実チップにTSVを形成して積層する場合に比べるとコストの上昇を抑えられる。またシリコン基板の上にシリコンダイを載せるので、熱膨張係数の違いによる信頼性の問題が生じないという利点がある。

ただし、微細なバンプでシリコンダイとシリコンインターポーザを接続したり、シリコン基板を追加したりといったコストは、用途によっては無視できない。比較的高めのシステムコストを許容できる高性能コンピューティング分野でCoWoS技術は製品化された。しかしシステムコストが低いモバイル端末分野では、CoWoS技術は高価すぎて受け入れづらい。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

- パワー停滞も光デバイス堅調、三菱電機の半導体部門