EE Times Japan >

プロセス技術 >

2.5D(2.5次元)の新世代パッケージング技術:福田昭のデバイス通信(104) TSMCが解説する最先端パッケージング技術(3)(2/2 ページ)

» 2017年04月17日 11時30分 公開

[福田昭,EE Times Japan]

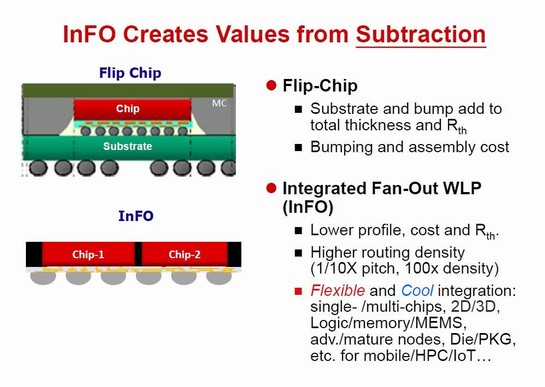

樹脂基板とバンプ、シリコンインターポーザを省く

そこでTSMCが開発したのが、「InFO(Integrated Fan-Out wafer level packaging)」と呼ぶ2.5次元のパッケージング技術である。

InFO技術の最大の特徴は、樹脂基板とバンプを省いたことだ。CoWoS技術から見ると、シリコンインターポーザも省いている。しかも、シリコンインターポーザに近い密度の再配線構造を形成することで、複数のシリコンダイを横に並べて集積可能にした。樹脂基板とバンプを省くことで材料コストと接続コストが下がり、高密度な再配線構造を形成することで小型化と薄型化を実現した。

InFO技術をフリップチップCSPと比べると、配線ピッチは約10分の1になり、配線密度は約100倍になっている。またシリコンダイとシリコンダイだけでなく、モールド樹脂封止済みパッケージやMEMSデバイスなどと組み合わせることも可能である。モバイル端末はもちろんのこと、IoT(モノのインターネット)端末や高性能コンピューティングなどにも応用可能な、最新世代のパッケージング技術だと言えよう。

ちなみにInFO技術はAppleのスマートフォン「iPhone 7」向けプロセッサ「A10」に採用されたほか、同社の次期プロセッサ「A11(仮称)」にも採用される見込みだ(関連記事:「TSMC、Apple「A10/A11」をほぼ独占的に製造か」)。

(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

中身が大変身した「iPhone 7」とその背景

中身が大変身した「iPhone 7」とその背景

2016年9月に発売されたAppleの新型スマートフォン「iPhone 7」。一部では、あまり目新しい新機能が搭載されておらず「新鮮味に欠ける」との評価を受けているが、分解して中身をみると、これまでのiPhoneから“大変身”を果たしているのだ。今回は、これまでのiPhoneとiPhone 7の中身を比較しつつ、どうして“大変身”が成されたのかを考察していこう。 TSMC、3nmチップの工場建設計画を発表

TSMC、3nmチップの工場建設計画を発表

TSMCが5nmおよび3nmチップの製造工場を新たに建設する計画を発表した。大手ファウンドリー各社のプロセス開発競争は激化の一途をたどっている。 Samsung、10nmプロセス技術開発でTSMCをリード

Samsung、10nmプロセス技術開発でTSMCをリード

半導体分野のアナリストによると、10nmプロセスの開発では、Intel、Samsung Electronics、TSMCが三つどもえ戦を繰り広げているが、現在はSamsungが一歩先を行っているようだ。 シリコンが次の手、村田製作所のキャパシター戦略

シリコンが次の手、村田製作所のキャパシター戦略

2016年10月に村田製作所が買収したフランスのIPDiAは、シリコンキャパシターを事業として手掛けるほぼ唯一のメーカーだ。積層セラミックコンデンサーに比べてかなり高価なシリコンキャパシターは、その用途は限られている。それにもかかわらず、なぜ村田製作所はIPDiAの買収に至ったのか。 FinFETサイズの物理的な限界は?

FinFETサイズの物理的な限界は?

ベルギーで開催された「IMEC Technology Forum(ITF) 2016」では、2.5D(2.5次元)のチップ積層技術や、FinFETのサイズの物理的な限界についても触れられた。 「iPhone 7 Plus」を分解

「iPhone 7 Plus」を分解

2016年9月16日に発売されたApple(アップル)のスマートフォン「iPhone 7 Plus」を、iFixitが分解した。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- 最新ノートPC5機種を分解 新旧MacBook Proの中身の違いは?

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- 「装置は動くがプロセスが成立しない」――He供給危機とナフサ不足の本質

- 次世代パワー半導体 「期待の5材料」の現在地

- He/ナフサ供給危機で工場新設も遅延? 装置/チップメーカーへの波及経路を探る

- Apple新CEOはエンジニア出身 製品開発重視への回帰か

- ルネサス26年1Qは増収増益 車載/AI好調で「足元は当面強い」

Special SitePR

あなたにおすすめの記事PR