バンプレスTSV配線、熱抵抗は従来の3分の1:3〜4倍のDRAM積層を可能に(1/2 ページ)

東京工業大学は、バンプレスTSV配線技術を用いると、3次元積層デバイスの熱抵抗を従来のバンプ接合構造に比べて3分の1にできることを明らかにした。メモリチップに適用すると、より多くのチップを積層することが可能となり、大容量化を加速する。

3次元積層デバイスの進化を支える垂直配線技術

東京工業大学科学技術創成研究院未来産業技術研究所の大場隆之教授らは2017年4月、バンプレスTSV(シリコン貫通ビア)配線技術を用いると、3次元積層デバイスの熱抵抗を従来のバンプ接合構造に比べて3分の1にできることを明らかにした。この技術をメモリチップに適用すると、従来に比べて3〜4倍の数量を積層することができ、大容量化が容易になるとしている。

今回の研究は大場氏と、東京工業大学を中心に半導体の設計技術やプロセス開発、製造装置、材料などの関連企業および研究機関などから成る研究グループ「WOW(Wafer On Wafer)アライアンス」が共同で行った。

大場氏らの研究グループは、極めて薄いウエハーを積層し、TSVで直接上下チップを接続配線する「バンプレスTSV配線」を開発している。今回は、そのバンプレスTSV配線と従来のバンプ接合TSV配線を行った3次元積層デバイスの熱抵抗について、有限要素法(FEM)と熱回路網の計算手法を用いて解析を行った。

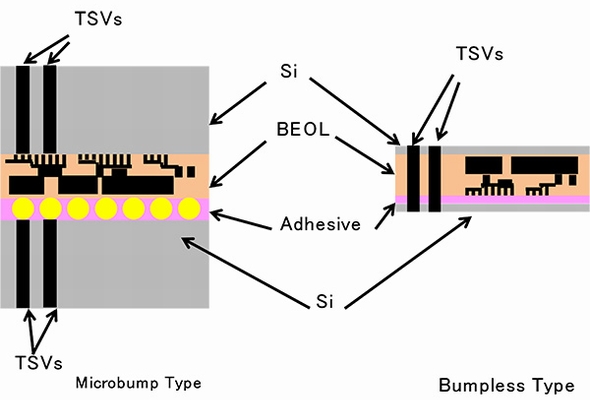

熱抵抗の解析に用いた3次元積層デバイスは、シリコン基板、TSV設置シリコン基板、BEOL(Back End of Line)および垂直方向の接合構造(マイクロバンプ構造またはバンプレス構造)などで構成される。今回は、BEOLと垂直接合部の熱抵抗に関して、FEMで熱伝導率を推定した。全体の熱抵抗は熱回路網を用いて推定した。

総合的な熱抵抗を推定する際に、マイクロバンプ構造の熱抵抗は、「IEEE SEMI-THERM Symposium 2013」でASET(超先端電子技術開発機構)の松本圭司氏らが発表した論文の計算手法を参考にした。これにより、直径25μmのマイクロバンプを50μmピッチで配置した時の熱抵抗は、全体で1.54Kcm2/Wになると算出できた。しかも、熱抵抗が高くなる要因のほとんどが、BEOLと垂直配線の接合構造であることが分かった。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

左がマイクロバンプタイプ、右がバンプレスタイプの断面構造 出典:東京工業大学

左がマイクロバンプタイプ、右がバンプレスタイプの断面構造 出典:東京工業大学